SPI Master Slave IP

Filter

Compare

105

IP

from

29

vendors

(1

-

10)

-

Serial Peripheral Interface – Master/Slave with Octal, Quad, Dual and Single SPI Bus support

- Operates with 8, 16 and 32 bit CPUs

- Full duplex synchronous serial data transfer

- DMA support

- Support for 32, 16 and 8 bit systems

-

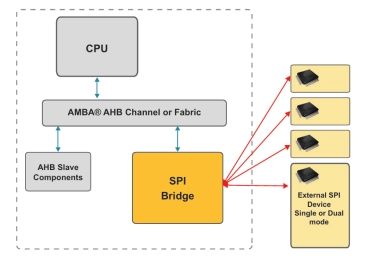

AHB-Lite Slave to SPI Master

- The AHB-Lite to SPI Bridge is used to translate 32-bit AHB-Lite Writes and Reads to Writes and Reads over a SPI interface. A custom 32-bit protocol is implemented on the SPI bus.

- The AHB-Lite to SPI Bridge has two AHB-Lite Slave component interfaces; one for access to the control/status registers (Register Interface), and another for access to the external SPI device (External Interface).

- The Bridge also has a SPI interface that operates exclusively as a SPI Master component device.

-

Master and Slave SPI Bus Controller

- Run-time programmable Master or slave mode operation.

- Bit rates generated in Master mode: ÷2, ÷4, ÷6, ÷8, ÷10, ÷12, ...÷512 of the system clock.

- Bit rates supported in Slave mode: fSCK ≤ fSYSCLK ÷4

- Support for 1,2,4 or unlimitted bytes multi-byte frame data transfers, run-time programmable.

-

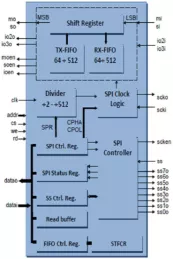

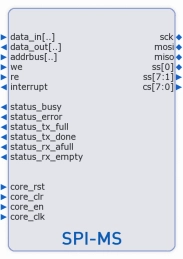

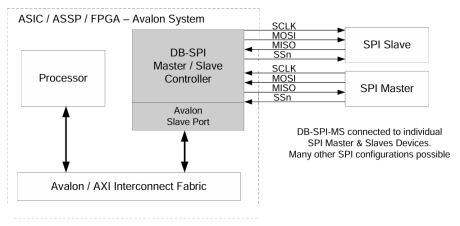

SPI Controller IP- Master/ Slave, Parameterized FIFO, Avalon Bus

- The Digital Blocks DB-SPI-MS-AVLN is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting both Master/Slave SPI Bus transfers.

- The DB-SPI-MS contains an Avalon Bus Interface for interfacing a microprocessor to external SPI Master/Slave devices.

-

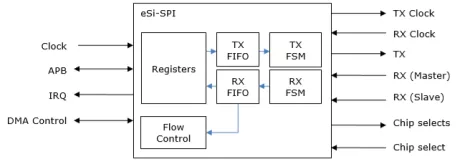

APB SPI (Serial Peripheral Interface) master and slave

- Master or slave operation.

- Programmable word size (1 to 32 bits).

- Programmable bit ordering (MSB first / LSB first).

- Programmable clock polarity (CPOL) and phase (CHPA).

-

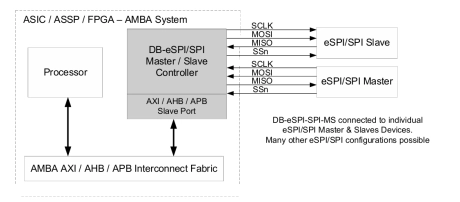

Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- The DB-eSPI-SPI-MS-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting the addition of Enhanced SPI (eSPI) bus transfers to the standard SPI Master/Slave Controller. The DB-eSPI-SPI-MS contains an AMBA AXI, AHB, or APB Bus Interface for interfacing a microprocessor to external eSPI or SPI Master/Slave devices.

- The DB-eSPI-SPI-MS contains both eSPI and SPI Master and Slave functions.

-

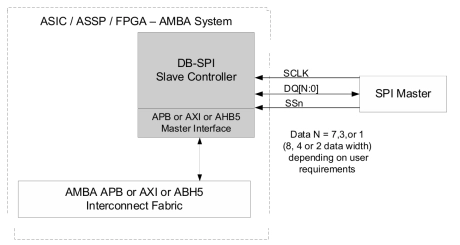

SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect

- The DB-SPI-S-AMBA-BRIDGE is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting only Slave SPI Bus transfers (both Full Duplex and Half Duplex) to/from a AMBA APB, AXI, or AHB Interconnect.

- The DB-SPI-S-AMBA-BRIDGE contains dual clock Transmit/Receive FIFOs and Finite State Machine control to process incoming SPI transmit/receive transactions, and a AMBA Master Interface (i.e. APB, AXI, AHB5) to read or write the SPI payload data with respect to the AMBA Interconnect. No processor is required for configuration or control; the DB-SPI-S-AMBA-BRIDGE operates autonomously from reset.

-

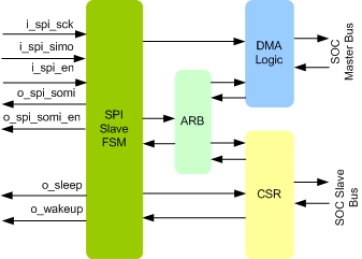

SPI Slave To SOC Bridge IIP

- Compliant with the SPI Block Guide 4.01 standard.

- Full SPI Slave functionality.

- Converts SPI Transactions into SOC write or read access.

- Allows external devices to access the internal SOC Bus

-

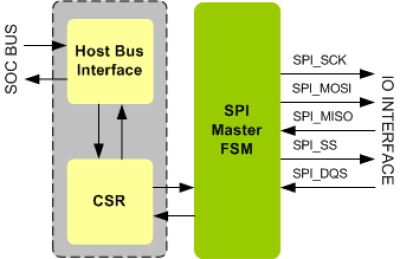

SPI Master IIP

- Compliant with SPI Block Guide 4.01 Standard

- Complaint to TI and National Modes (Microwire)

- Supports 3 wire and 4 wire operation

- Supports DDR mode of operation

-

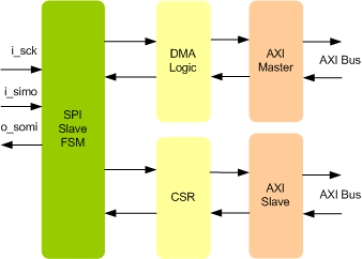

SPI Slave To AXI Bridge IIP

- Compliant with the SPI Block Guide 4.01 standard.

- Full SPI Slave functionality.

- Converts SPI Transactions into AXI write or read instructions

- Allows external devices to access the internal AXI Bus