SATA Controller IP

Filter

Compare

166

IP

from

25

vendors

(1

-

10)

-

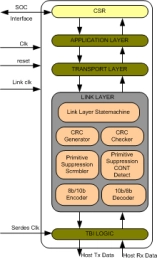

SATA Controller IP Core

- Data transfer speed is compliant with SATA 1.5-Gbps and 3.0-Gbps industry specifications

- Both Host and Device modes are supported

- Compact design with a resource usage of 1200 Slice LUTs

- Synchronous design for easy integration

-

SATA HOST CONTROLLER IIP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

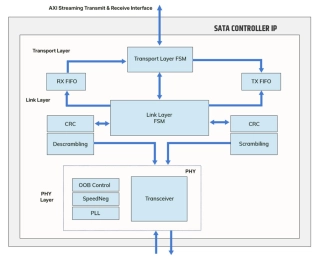

SATA 3 Controller IP

- Simple AXI streaming TX and RX interface for application layer communication.

- It supports Native Command Queuing and key primitives/FIS types from SATA specifications.

- Compliant with Serial ATA 3.0 specification.

- Supports data rates of 1.5/3/6 Gbit/s.

-

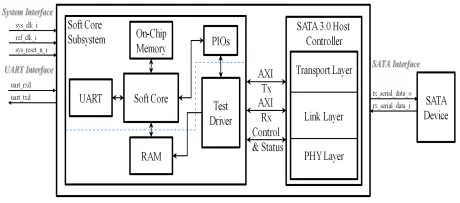

SATA HOST Controller

- Designed to SATA v3.0 (6Gbps)

- Low Latency: 66K IOPS Read, 67K IOPS Write (4k blocks)

- Connects to SAPIS compliant serial ATA Phy

- Manage SATA reference frequency difference between the FPGA and the Disk

-

-

SATA Host Controller

- SATA Spec Rev2.6 compatible Link and Transport layer

- Supports 1.5Gbps and 3Gbps data rates

- Compliant to AHCI 1.1, support one port

- Supports Native Command Queuing (FPDMA)

-

SATA 6G Host Controller IP

- Compliant with SATA/eSATA v3.3 and SATA PIPE v4.3 specifications

- Memory data protection and memory address parity protection

- Hardware support for native nommand queuing (NCQ)

- End-to-end parity data path protection

-

SATA 3G Host Controller IP

- Compliant with SATA/eSATA v3.3 and SATA PIPE v4.3 specifications

- Memory data protection and memory address parity protection

- Hardware support for native nommand queuing (NCQ)

- End-to-end parity data path protection