RISC-V Tensor unit IP

Filter

Compare

4

IP

from

3

vendors

(1

-

4)

-

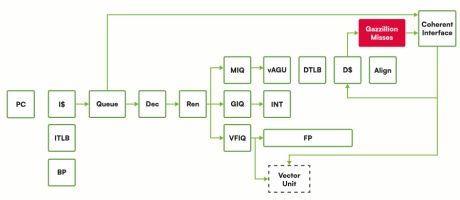

Fully-coherent RISC-V Tensor Unit

- The bulk of computations in Large Language Models (LLMs) is in fully-connected layers that can be efficiently implemented as matrix multiplication.

- The Tensor Unit provides hardware specifically tailored to matrix multiplication workloads, resulting in a huge performance boost for AI without a big power consumption.

-

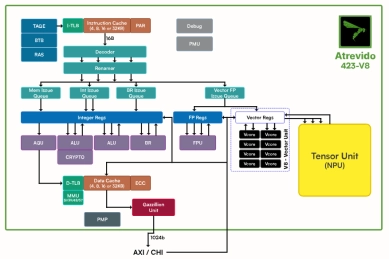

64-bit Out-of-Order RISC-V Customisable IP Core

- Ready for the most demanding workloads, Atrevido supports large memory capacities with its 64-bit native data path. With its complete MMU support, Atrevido is also Linux-ready, including multiprocessing.

-

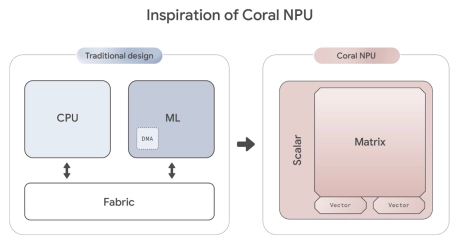

RISC-V-Based, Open Source AI Accelerator for the Edge

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.

-

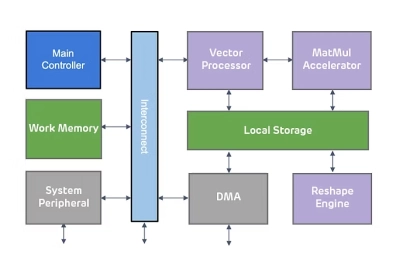

Highly scalable inference NPU IP for next-gen AI applications

- ENLIGHT Pro is meticulously engineered to deliver enhanced flexibility, scalability, and configurability, enhancing overall efficiency in a compact footprint.

- ENLIGHT Pro supports the transformer model, a key requirement in modern AI applications, particularly Large Language Models (LLMs). LLMs are instrumental in tasks such as text recognition and generation, trained using deep learning techniques on extensive datasets.