PCIe PHY IP

Filter

Compare

671

IP

from

51

vendors

(1

-

10)

-

PCIe PHY and controller solution

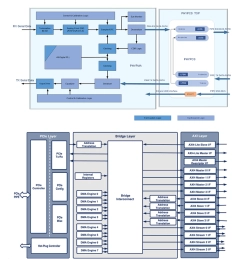

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

PCIe PHY

- Support for PCIe3(8.0Gbps),Backward compatible with 2.5Gbps and 5Gbps for PCIe

- Full compatible with PIPE4.2 interface specification

- Support 16bit and 32bit parallel data bus

- Independent channel power down control

- Supported reference clock input range from 25M to 400M

-

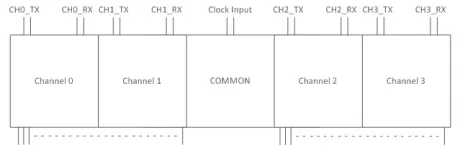

1-lane to 4-lane PCIE PHY

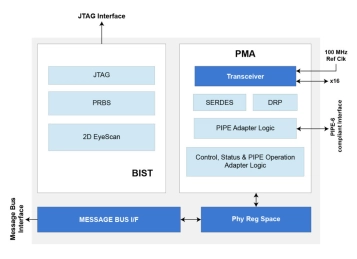

- This 1-lane to 4-lane PCIE PHY includes all high-speed analog functions for high-speed data transport between chips over PCBs and high quality cables.

- It can support different data rates (2.5Gbps to 8Gbps) for compatible with PCIe1.1, PCIe2.1 and PCIe3.1 protocols.

- It is optimized for low power operation and is suitable for 8b, 10b, 16b, 20b input data path width.

- For long trace signal transmission, the PCIe PHY contains programmable 3-tap FFE, CTLE and 5-tap DFE with adaptive algorithm.

- In-built Eye Monitor can help analysis internal high-speed signal and BIST function is useful for production test.

-

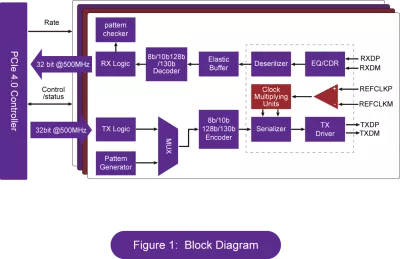

PCI Express 4.0 PHY

- Compiles with PCIe 4.0, 3.1, 2.1, 1.1 and PIPE 4.4.1 specifications

- Supports all power-saving modes (P0, P0s, P1, P2) as defined in PIPE 4.4.1 specifications

- Supports L1 PM/CPM substates with CLKREQ#

- Supports the separate REFCLK Independent SSC (SRIS) architecture

-

PCIe GEN6 PHY IP

- The PCIe GEN6 PHY IP achieves data rates up to 64GT/s per lane with PAM4 signaling thereby delivering reliable performance for high-speed data transfer.

- It supports advanced applications, including AI/ML, High-Performance Computing, and next-generation storage solutions.

-

Low Power PCIe Gen3 PHY on TSMC CLN16FFC

- Industry leading low power PMA macro – 36mW per lane at 8Gbps (4.5mW/Gbps), inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.133 mm2 total active area per lane

- Supported protocols include: PCIe Gen3/2/1, SATA3/2/1, XAUI/RXAUI, SGMII

- Finely configurable receiver impedance, CTLE gain and bandwidth, with fully adaptive CTLE and 5- tap DFE

-

Low Power PCIe Gen3 PHY on TSMC CLN12FFC

- Industry leading low power PMA macro – 39mW per lane at 8Gbps (4.88mW/Gbps), inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.133 mm2 total active area per lane

- Supported protocols include: PCIe Gen3/2/1, SATA3/2/1, XAUI/RXAUI, SGMII

- Finely configurable receiver impedance, CTLE gain and bandwidth, with fully adaptive CTLE and 5- tap DFE

-

PHY for PCIe 7.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

PCIe 2.0 PHY, UMC 40LP, x1

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island