PCIe Gen 4.0 PHY IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

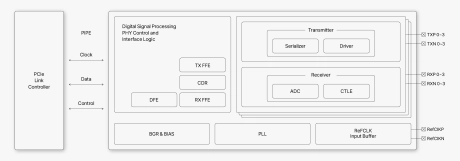

PCI Express Gen 4 PHY

- Support 16GT 8GT 5GT 2.5GT data rate

- Compliant with PCI Express 4.0, 3.1, 2.1, 1.1 and PIPE 4.2 standards

- x1, x2, x4, x8, x16 lane configuration with bifurcation

- Multi-tap adaptive programmable continuous time linear equalizer (CTLE) and decision feedback equalizer (DFE)

-

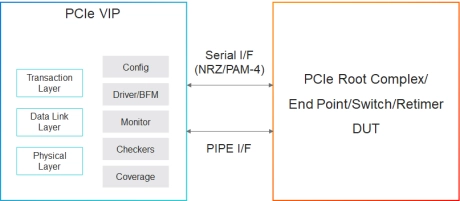

PCIe Gen 5 Verification IP

- Support for 32.0 GT/s Data Rate per lane with backwards compatible.

- Optimizing the Link to skip equalization at lower Data Rates when supporting 32.0 GT/s(optional feature).

- Lower pin count in pipe interface when supporting 32.0 GT/s.

- Support for newly added phy serdes architecture in pipe specification 5.0 .

-

PCIe Gen5/6 PHY IP

- Best-in-class Power / Performance / Area competitiveness

- Compliant to PCIe 5.0/6.x Base specification

- Supports lane configurations according to the customer’s demands

- Supports data rates of 2.5GT/s, 5.0GT/s, 8.0GT/s, 16GT/s, 32GT/s and 64GT/s (PAM4)

-

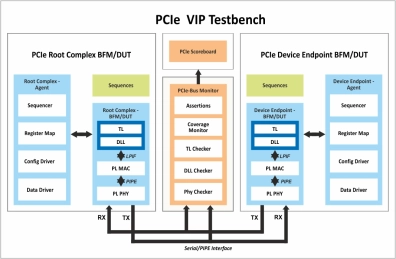

Simulation VIP for PCIe

- Device Type

- Root Complex, End Point, Legacy End Point, Switch, PHY DUT, Bridge

- Interface

- Serial, Parallel (8-bit, 10-bit, 128-bit, and 130-bit), PIE8, PIPE 3.0, PIPE 4.0, PIPE 4.3, PIPE 4.4.x, PIPE 5.x, PIPE 6.0

-

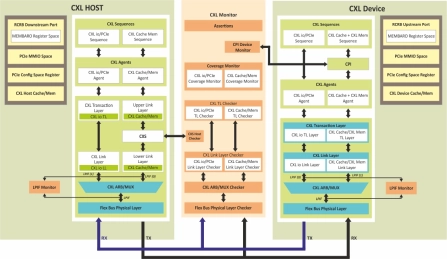

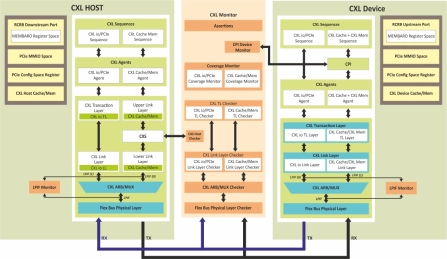

CXL 4 Verification IP

- Compliant with the CXL 4, 3.2, 2.0 & 1.1 Specifications.

- Support for all three protocols CXL.IO, CXL.CACHE & CXL.MEM including all CXL device types

- Support for PCIE Mode & Alternate Protocol Negotiation for CXL Mode

- Support for 256B flit in 128GT/s with PCIe Gen 6 as well as 64/32/16/8 GT/s speeds with backward compatibility.

-

CXL 4.0/3.2/3/2 Verification IP

- Compliant with the CXL 3.2, 2.0 & 1.1 Specification.

- Support for all three protocols CXL.IO, CXL.CACHE & CXL.MEM including all CXL device types

- Support for PCIE Mode & Alternate Protocol Negotiation for CXL Mode

- Support for 256B flit in 64GT/s with PCIe Gen 6 as well as 32/16/8 GT/s speeds with backward compatibility.