MIPI D-PHY PHY IP

Filter

Compare

364

IP

from

32

vendors

(1

-

10)

-

MIPI D-PHY TX PHY and DSI controller

- Scalability and Flexibility: Supports multiple data lanes for higher aggregate bandwidth, any of the multiple lanes can be configured into Clock Lane

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI D-PHY RX 2/4L

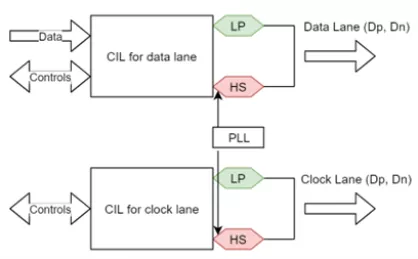

- ? Flexible input clock reference - 17 MHz to 27 MHz

- ? 50% DDR output clock duty-cycle

- ? Lane operation ranging from 80 Mbps to 1.5 Gbps in forward direction

- ? Aggregate throughput up to 3 Gbps with two data lanes, 6 Gbps with four data lanes

-

MIPI D-PHY Bidir 2/4L

- ? Attachable PLL clock multiplication unit for master-side functionality

- ? Flexible input clock reference — 5 MHz to 500 MHz

- ? 50% DDR output clock duty-cycle

- ? Lane operation ranging from 80 Mbps to 1.5 Gbps in forward direction

-

MIPI D-PHY v2.1 IP Core

- Compliant to MIPI® Alliance Standard for D-PHY specification Version 2.1

- Supports D-PHY 1.1 synchronous transfer mode at high speed mode with a bit rate of 80-1500 Mb/s without deskew calibration

- Supports DPHY 1.2 for 1500 – 2500 Mb/s with deskew calibration.

-

MIPI D-PHY Analog Transceiver IP Core

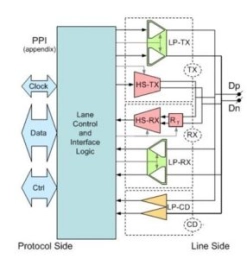

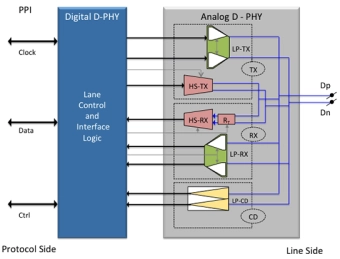

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

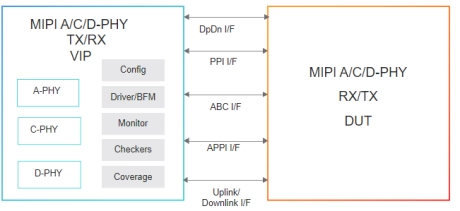

MIPI D-PHY Verification IP

- Compliant to MIPI D-PHY Specification Version 3.5 with PPI interface.

- Support HS-IDLE State between two data burst.

- Support for Alternate calibration Sequence & Preamble sequence.

- Supports all possible configuration for Data Lane Module and Clock Lane Module at PHY layer.

-

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

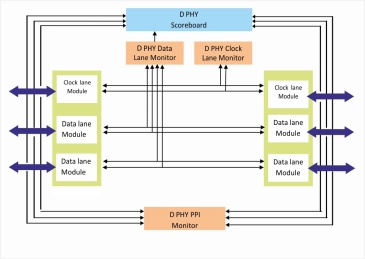

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

MIPI D-PHY

- Physical interface for CSI-2 and DSI providing 2.5Gbps per lane of bandwidth

- MIPI D-PHY Analog Transceiver IP Core is fully compliant to the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

MIPI D-PHY TX & RX + DSI & CSI Controllers

- Compliant with MIPI Committee Specifications

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Display Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI DPHY v1.2 TX 4 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes