MIPI D-PHY IP

Filter

Compare

454

IP

from

40

vendors

(1

-

10)

-

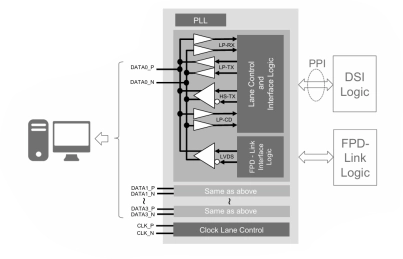

MIPI D-PHY and FPD-Link (LVDS) Combinational Transmitter for TSMC 22nm ULP

- Technology is TSMC 22nm ULP 1p10M.

- Supply voltage can be applied 1.0V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode for MIPI D-PHY Transmitter.

- Data rate of each channel is 609Mbps for FPD-Link(LVDS).

-

MIPI D-PHY v2.1 IP Core

- Compliant to MIPI® Alliance Standard for D-PHY specification Version 2.1

- Supports D-PHY 1.1 synchronous transfer mode at high speed mode with a bit rate of 80-1500 Mb/s without deskew calibration

- Supports DPHY 1.2 for 1500 – 2500 Mb/s with deskew calibration.

-

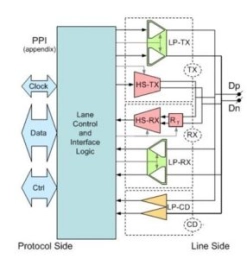

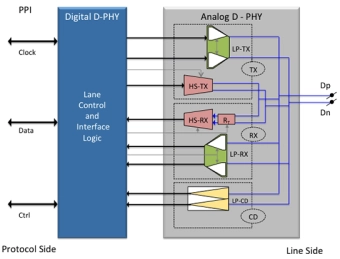

MIPI D-PHY Analog Transceiver IP Core

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

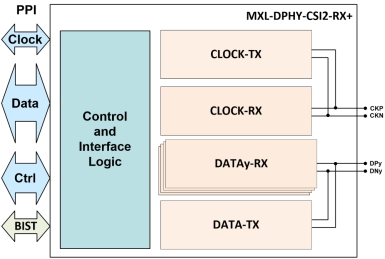

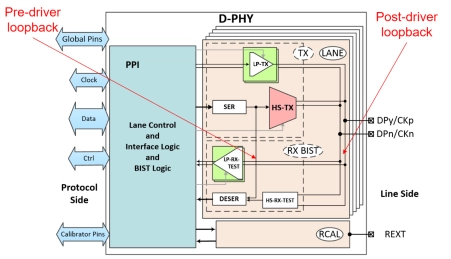

MIPI D-PHY RX+ (Receiver) IP

- The MIPI® D-PHY RX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Receiver.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

MIPI D-PHY TX+ (Transmitter)

- The MIPI® D-PHY TX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Transmitter.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

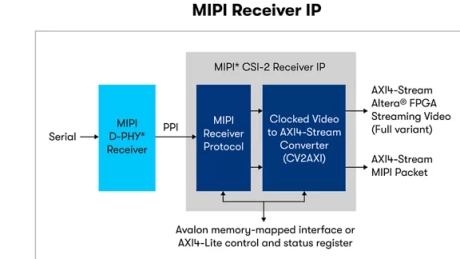

MIPI D-PHY IP

- Mobile Industry Processor Interface (MIPI) D-PHY is supported on Agilex™ 5 and Agilex™ 3 FPGAs allowing transmission and reception of data through PHY-protocol interface (PPI) to connect with camera serial interface (CSI) and display serial interface (DSI) applications.

-

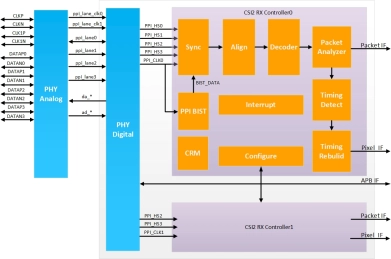

MIPI D-PHY1.2 CSI/DSI TX and RX

- The MIPI D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It supports MIPI D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

- It enables seamless connectivity with D-PHY based sensors, making it ideal for SoCs in consumer electronics, automotive, and IoT devices

-

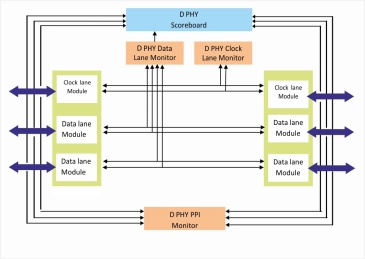

MIPI D-PHY Verification IP

- Compliant to MIPI D-PHY Specification Version 3.5 with PPI interface.

- Support HS-IDLE State between two data burst.

- Support for Alternate calibration Sequence & Preamble sequence.

- Supports all possible configuration for Data Lane Module and Clock Lane Module at PHY layer.

-

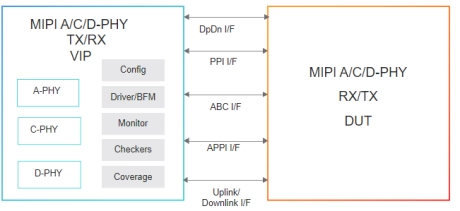

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

MIPI D-PHY

- Physical interface for CSI-2 and DSI providing 2.5Gbps per lane of bandwidth

- MIPI D-PHY Analog Transceiver IP Core is fully compliant to the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.