MIPI C/D-PHY IP

Filter

Compare

31

IP

from

8

vendors

(1

-

10)

-

MIPI C/D-PHY CSI/DSI TX and RX

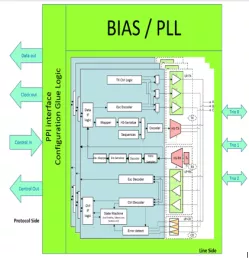

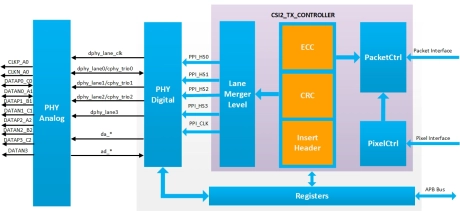

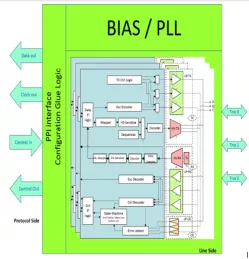

- The MIPI C/D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It integrates C-PHY and D-PHY in a single IP core, supporting both MIPI C-PHY 1.1 and D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

-

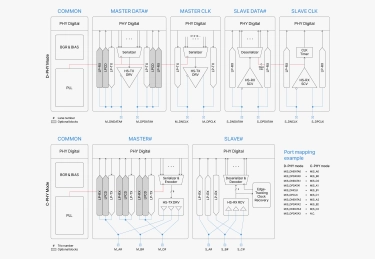

MIPI C/D-PHY Combo IP

- Compliant to MIPI D-PHY v3.0, C-PHY v2.1 specification

- Area efficient macro optimized for placement for dense SoC designs

- Support Uni-(TX or RX) and Bi-directional(TX and RX) mode

- Support emphasis architecture over lossy channel for TX

- Support equalize architecture over lossy channel for RX

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 40 LP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 40 LP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 28 HPC+

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 28 HPC+

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 22 ULP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 22 ULP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 16 FFC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 16 FFC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode