ISO26262 CAN IP

Filter

Compare

64

IP

from

13

vendors

(1

-

10)

-

CAN 2.0, CAN FD - Developed as ISO26262-10 Safety Element out of Context (ISO26262 soft IP SEooC, ASIL-B ready design)

- Designed in accordance to ISO 11898-1:2015

- Supports CAN 2.0B and CAN FD frames

- Support up to 64 bytes data frames

-

CAN XL Controller

- Designed in accordance with ISO 11898-1:2024 specification (tbc) and CiA610-1 specification

- Supports CAN, CAN FD and CAN-XL frames

-

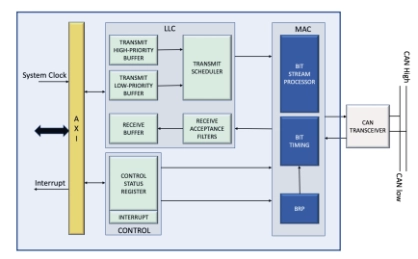

Configurable CAN Bus Controller with Flexible Data-Rate

- Designed in accordance with ISO 11898-1:2015 specification

- Supports CAN and CAN FD frames

- Supports up to 64 bytes of data frame

-

CAN CC, CAN FD, and CAN XL Bus Controller

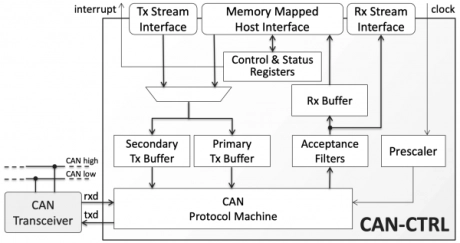

- The CAN-CTRL implements a highly featured and reliable CAN bus controller that performs serial communication according to the Controller Area Network (CAN) protocol.

- It supports classical CAN and CAN FD according to ISO 11898-1:2015; CAN XL as specified in CiA 610-1 specification; Time-Triggered CAN (TTCAN) per ISO 11898-4; and CAN Frame time-stamping as described in the CiA 603 profile.

- This CAN controller core handles data rates exceeding 20Mbit/s and it is optimized for the AUTOSAR and SAE J1939 specifications.

-

CAN-XL Bus Controller IP

- The CAN-XL Bus Controller Core performs serial communication as per CAN 2.0, CAN-FD & CAN-XL Specifications.

- It also supports original Bosch Protocol & ISO 11898 specifications for TTCAN (Time Triggered Operation) as specified in ISO11898-4.

- The design is fully optimized to support AUTOSAR and SAE J1939 specifications.

-

-

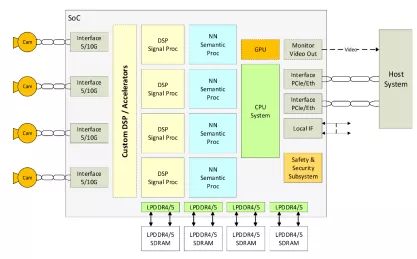

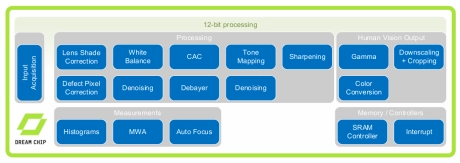

Real-time Pixel Processor for Vision applications

- The H Series provides configurable input and output data widths. It accepts YCbCr or RAW input data and supports input image frames with 8, 10 and 12-bit amplitude resolutions.

- The H1 Series are ISPs which are optimized for area while getting the best image quality.

- Options to extend the pipeline with a Machine Vision output or configuring the line size to further optimize area are possible.

-

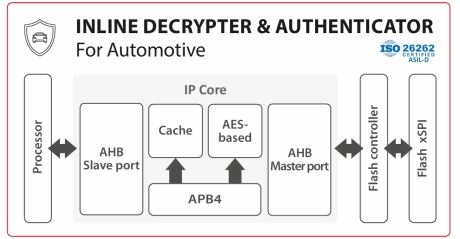

Inline Decrypter & Authenticator IP Core for Automotive

- The Inline Decrypter and Authenticator IP core enables on-the-fly execution of encrypted and signed code from Flash.

- It is used to authenticate and decrypt code located in Flash. In addition it is ISO26262 certified (ASIL-D).

-

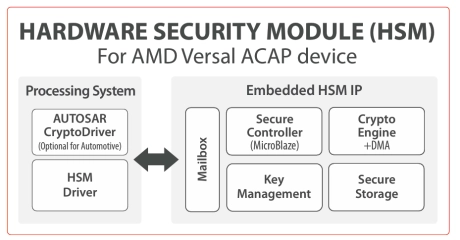

Hardware Security Module (HSM) for AMD Xilinx Versal ACAP device

- The HSM IP module is a Hardware Security Module for a wide range of applications.

- It is developed according to the guidelines set out by the EVITA project and is meant to be implemented on a AMD Xilinx Versal ACAP device.

- It supports TrustZone.

-

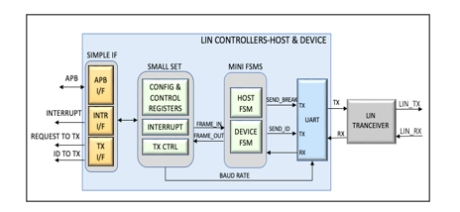

Host / device LIN controller IP

- The LIN Controllers IP– Local Interconnect Network Controllers IPs are compliant to LIN 2.0, 2.1 & 2.2A Specifications. Backward compliant to LIN 1.3 Specification as well.

- These can be integrated into systems through various simple AMBA-APB, AMBA-AHB or SRAM like interfaces that require LIN connectivity commonly used in automotive and industrial applications.