ISO 26262 ASIL B IP

Filter

Compare

266

IP

from

12

vendors

(1

-

10)

-

ASIL B / ISO 26262 and ISO 21434 Compliant 1G-25G MACsec Security Module

- Synopsys MACsec Security Modules use scalable AES-GCM cryptography to provide confidentiality, integrity, authentication, and replay protection for Ethernet traffic.

- These modules integrate seamlessly with Synopsys Ethernet MAC & PCS IP, supporting high data rates with low latency. By incorporating Synopsys MACsec Security Modules into Ethernet IP solutions, networking SoC designers can ensure end-to-end security for data in motion between Ethernet-connected devices.

-

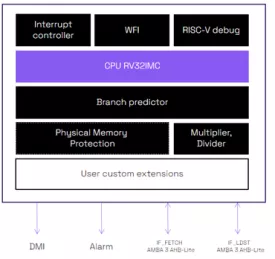

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Flexible use cases

- roven technology

- State-of-the-art safety and security

-

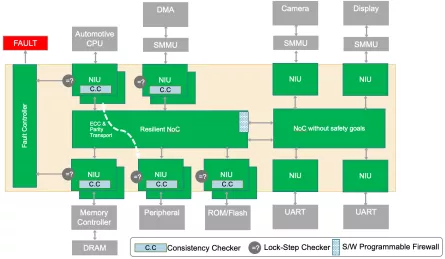

FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.

- ARM® Cortex®-R5 and Cortex-R7 processor port checking

- Hardware duplication and redundancy

- Custom ECC and parity generation and checking

-

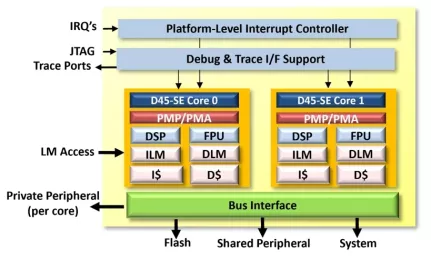

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

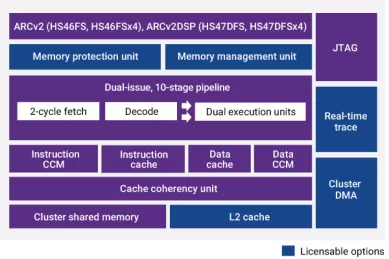

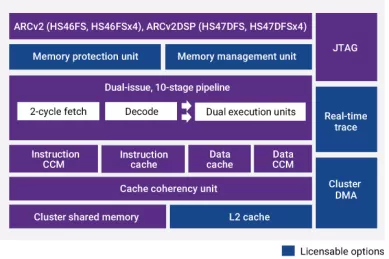

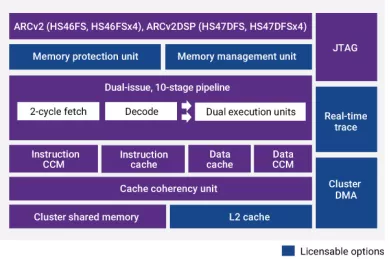

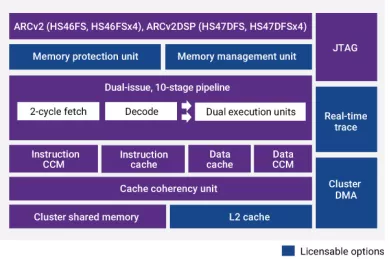

ARC Functional Safety (FS) Processor IP supports ASIL B and ASIL D safety levels to simplify safety-critical automotive SoC development and accelerate ISO 26262 qualification

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- Supports MIPI - Camera Service Extensions CSE 2.0 specification

- Automotive‑ compliant: ISO 26262 (ASIL‑B) & ISO 21434

- Plug‑and‑play with Synopsys CSI‑2 Host Controllers

- Data integrity protection and optional encryption (AES-CMAC, AES-GMAC, AES-CTR)

-

ARC HS48FSx4 quad-core, host processor , ASIL B / ASIL D support, incl. lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS48FS, host processor, with ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS47DFSx4 quad-core, w/ DSP extensions, ASIL B / ASIL D support, incl. lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS47DFS, with DSP extensions, and ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor