H.264 Encoder IP

Filter

Compare

48

IP

from

15

vendors

(1

-

10)

-

H.264 Encoder

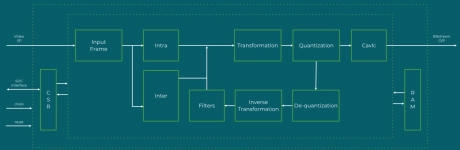

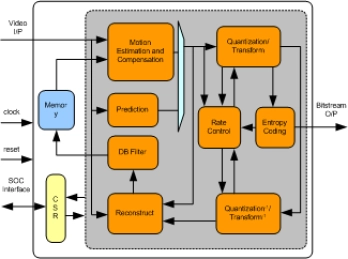

- The H.264 Encoder IP Core delivers a high-performance video compression solution ideal for applications such as surveillance, broadcast, mobile, and automotive systems.

- Fully compliant with the ITU-T H.264/AVC standard, it enables efficient encoding of video streams with excellent visual quality and reduced bandwidth requirements.

-

H264 ENCODER IIP

- Supports ISO/IEC 14496-10/ITU-T H.264 specification.

- Supports full H.264/AVC Encoder functionality.

- Supports video resolution up to 3840x2160@60fps.

- Supports all type of prediction methods.

-

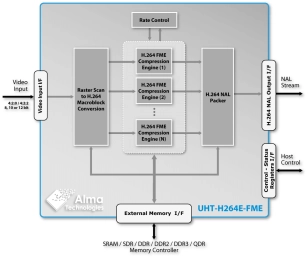

Scalable Ultra-High Throughput H.264 Encoder − Full Motion Estimation

- The UHT-H264E-FME core is a scalable, ultra-high throughput, hardware H.264 encoder, designed to enable 4K and 8K Ultra HD resolutions in power- and cost-effective FPGA or ASIC implementations.

- Powered by a highly-featured Full Motion Estimation engine, this encoder is the most advanced one of our UHT H.264 IP cores and offers best-in-class compression for applications needing advanced H.264 efficiency for high-quality, low-bitrate video encoding.

-

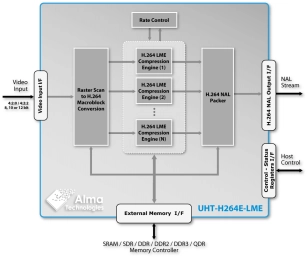

Scalable Ultra-High Throughput H.264 Encoder − Light Motion Estimation

- The UHT-H264E-LME core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.

-

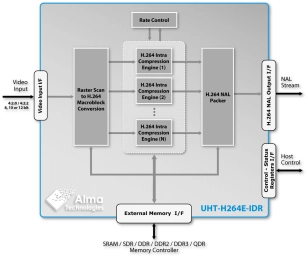

Scalable Ultra-High Throughput H.264 Encoder − Intra Frames (IDR) Encoding

- The UHT-H264E-IDR core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.

-

H.264 Encoder FPGA Core

- 1.5 clocks/pixel processing rate Fully compatible with the ITU-T H.264 specification Available with bus widths from 8-12 to handle deeper pixel depths (Pre-compiled for Binary license.) Supports resolutions up to 4096 x 4096 (can be expanded with additional cores) Supports simultaneous encoding of multiple streams of arbitrary sizes and compression ratios Generates I and P frames Variable Bit Rate (VBR) and Constant Bit Rate (CBR) Search range: 80 X 48 pixels, Full, 1/2, 1/4 pixel resolution Entropy Encoding: CAVLC Support for intra 4 x 4 DC prediction Support for Single or Multiple slices via firmware control Supports YUV 4:2:0 video input Fully synchronous design Available as FPGA specific netlist Custom versions available

- Recent Enhanced Features

- New improved AXI wrapper to simplify integration of core AXI stream for video input and compressed output Latency reduced from 1 frame to less than 1ms for a 1080p30 video stream LOWEST LATENCY IN THE INDUSTRY! Others quote low latency but limit it to I frame only. Our core is low latency and supports I and P frames! Significant reduction in Block RAM requirements for external raster to macroblock reordering

-

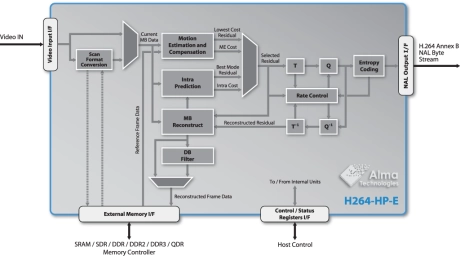

High Profiles H.264 Encoder − High 10, High 4:2:2 and High 4:4:4 (12-bit 4:2:2 or 4:2:0) Profiles

- The H264-HP-E core is an advanced and self-contained ITU-T H.264 High profiles hardware encoder.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports real time encoding of both single and multiple 4:2:0 and 4:2:2 video streams, in 8-, 10- or 12-bit per component color depth, up to Profile Level 5.2.

-

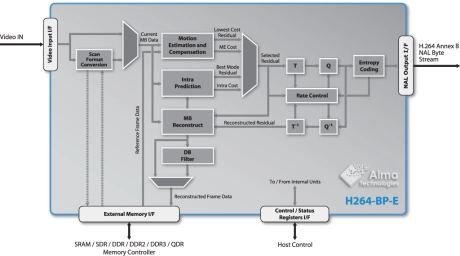

Baseline Profile H.264 Encoder

- The H264-BP-E core is an advanced self-contained hardware H.264 encoder that conforms to the ITU-T H.264 Constrained Baseline Profile.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports the real time encoding of both single and multiple 8-bit 4:2:0 video streams, up to Profile Level 5.2.

-

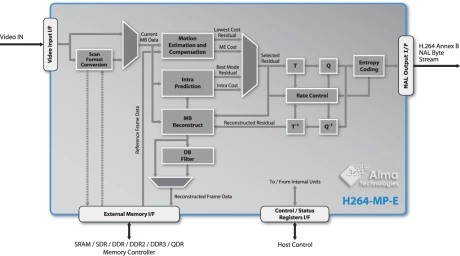

Main Profile H.264 Encoder

- The H264-MP-E core is an advanced self-contained hardware H.264 encoder that conforms to the ITU-T H.264 Main Profile.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports the real time encoding of both single and multiple 8-bit 4:2:0 video streams, up to Profile Level 5.2.

-

AVC (H.264) CABAC Encoder IP Core

- The CABAC Encoder IP Core is an RTL implementation of the lossless CABAC (Context-Adaptive Binary Arithmetic Coding) algorithm.

- This IP Core is specifically designed for hardware acceleration of entropy arithmetic coding in the AVC (H.264) video compression format.