GF 22FDX PLL IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

LPDDR4 multiPHY V2 - GF 22FDX

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

Ultra Low-Power High-Performance AFE on GF 22FDX

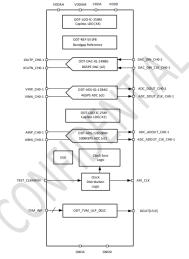

- The ODT-AFE-2T2R-GF22FDX is an ultra-highperformance AFE designed in a Global Foundries 22nm process.

- The AFE includes two 12-bit, 4GSPS I/Q ADC pairs, two 14-bit, 8GSPS I/Q DAC pairs, four capless LDOs, one Bandgap reference and one temperature sensor and includes an integrated 3rd party PLL.

-

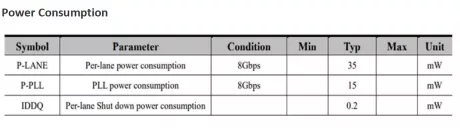

PCIe 3.0 Serdes PHY IP, Silicon Proven in GF 22FDX

- Silicon Proven in GF 22GDX with 0.8V and 1.8V power supply.

- Compatible with PCIe base Specification

- Support 32-bit/16-bit parallel interface

- Support for PCIe3(8.0Gbps)

-

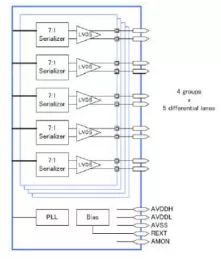

V-by-One/LVDS Tx IP, Silicon Proven in GF 22FDX

- Support data rate: 0.6Gbps~4.0Gbps

- Utilize per-lane 10bit parallel interface

-

Ring oscillator-based analog PLL

- Our ring oscillator-based analog PLL provides good phase noise performance with extremely low energy consumption and small area compared to the state-of-the-art products.

- The programmable divider allows to shift the output frequency with a large locking range.