Perceptia’s DeepSub™ pPLL03F is a family of all digital PLLs featuring low-jitter and compact area suitable for clocking applications with critical timing requirements at frequencies up to 4GHz. It is suitable as a clock source for performance computing blocks and ADCs/DACs with moderate SNR requirements.

Perceptia’s second generation pPLL03F family is available on technologies from 5nm to 40nm and across multiple foundry partners. We are continually expanding the range of technologies where it is silicon proven and can quickly port it to other technologies or foundries upon request.

To give SoC designers the maximum flexibility in building complex multi-domain clock systems, pPLL03F is very small (< 0.005 sq mm) and low power (< 2.1mW in GF 22FDX). It is well suited to applications with many clock domains where each is driven by their own PLL. To simplify system design, PLL03 has an integrated power supply regulator which allows multiple instances of PLL03 to share common power supplies. Alternatively instances of pPLL03 can share supplies with the blocks that use its output clock.

pPLL03 integrates easily into any SoC design and includes all the views and models required by modern back end flows.

The pPLL03F is built using Perceptia’s second generation all digital PLL technology. This robust technology delivers identical performance across many processes, regardless of PVT conditions. It consumes a small fraction of the area of an analog PLL whilst maintaining comparable performance.

pPLL03F can be used as an integer-N PLL or as a fractional-N PLL. The fractional-N mode provides a high flexibility to choose the best combination of input and output clock frequencies at the system level.

Perceptia further provides integration support and offers customization and migration services.

Fractional-N PLLs for Performance Computing

Overview

Key Features

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

- Second-generation digital PLL architecture, providing integer and fractional multiplication

- Two PLL outputs via separate postscalers

- Post-scalers programmable from 1 to 2,040

- Lock-detect output

- Can generate a spread-spectrum clock from a clean reference

- Oscillator output duty cycle better than 48 / 52% on CK_PLL_OUT0 and CK_PLL_OUT1

- Highly testable using industry standard flows

- ATPG vectors provided

- Specification of functional tests to supplement ATPG testing

- Industrial operating conditions (-40 to 85°C) with junction temperature up to 100°C

Benefits

- Fractional multiplication with frequency up to 5GHz (12nm and below) or 5GHz (16nm and above)

- Low jitter (< 10ps RMS)

- Small size (< 0.005 sq mm)

- Low Power (< 2.1mW in GF 22FDX)

- Support for multi-PLL systems with tens of PLLs per SoC

- Easy integration

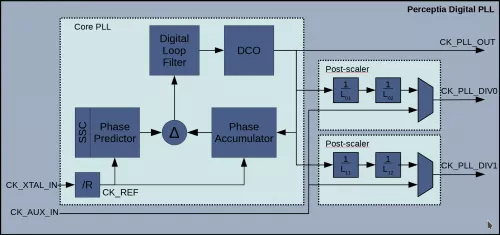

Block Diagram

Applications

- Performance Computing

- Complex SoCs with many clock domains

- Low-jitter applications

- Moderate SNR ADC/DAC

Deliverables

- Datasheet

- Detailed Verilog behavioral model

- Timing models

- LEF5.6 abstract for floor planning/chip assembly

- Integration Guide

- DFT Guide

- Integration support

- Characterization report

- GDSII layout macrocell

- CDL netlist for LVS

- DRC, LVS and SI verification reports

- Netlist model with accompanying documentation allowing integration of the module in scan chains

Technical Specifications

Short description

Fractional-N PLLs for Performance Computing

Vendor

Vendor Name

Foundry, Node

Portable to all CMOS processes 65nm and smaller. See specific product listings

Maturity

Silicon Proven

Availability

Depends on process - please ask

GLOBALFOUNDRIES

Pre-Silicon:

12nm

,

14nm

,

14nm

LPE

,

14nm

LPP

,

20nm

LPM

,

28nm

,

28nm

FDSOI

,

28nm

HPP

,

28nm

LPH

,

28nm

SLP

,

32nm

,

40nm

LP

,

55nm

,

55nm

LPX

,

65nm

,

65nm

LP

,

65nm

LPe

SMIC

Pre-Silicon:

14nm

,

28nm

,

28nm

HK

,

28nm

HKC+

,

28nm

PS

,

40nm

LL

,

55nm

G

,

55nm

LL

,

65nm

LL

Samsung

Pre-Silicon:

10nm

,

28nm

FDS

,

28nm

LPH

,

28nm

LPP

,

32nm

LP

,

45nm

LP

,

65nm

LP

TSMC

Pre-Silicon:

5nm

,

10nm

,

12nm

,

16nm

,

20nm

,

22nm

,

28nm

,

28nm

HP

,

28nm

HPC

,

28nm

HPCP

,

28nm

HPL

,

28nm

HPM

,

28nm

LP

,

40nm

G

,

40nm

LP

,

45nm

GS

,

45nm

LP

,

55nm

FL

,

55nm

G

,

55nm

GP

,

55nm

LP

,

55nm

NF

,

55nm

ULP

,

55nm

ULPEF

,

55nm

UP

,

65nm

G

,

65nm

GP

,

65nm

LP

UMC

Pre-Silicon:

14nm

,

28nm

,

28nm

HLP

,

28nm

HPC

,

28nm

HPM

,

28nm

LP

,

55nm

,

65nm

LL

,

65nm

LP

,

65nm

SP

Related IPs

- High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- General Purpose Fractional-N PLLs

- Fractional-N PLL for Performance Computing in GlobalFoundries 22FDX

- Fractional-N PLL for Performance Computing in GlobalFoundries 12LPP/14LPP

- Fractional-N PLL for Performance Computing in Samsung 8LPP

- Fractional-N PLL for Performance Computing in Samsung 14LPP