DMA Controller IP

Filter

Compare

388

IP

from

74

vendors

(1

-

10)

-

DMA Controller

- DTI_DMA control the DMA transfers data between different points in the memory space without intervention of the CPU.

- The DMA is generally used to replace two CPU functions: memory copy and transfer data between memory and peripheral (peripheral devices such as SPI, UART, GPIO, I2C, I2S, WDT, etc.)

-

Multi-Channel Streaming DMA Controller

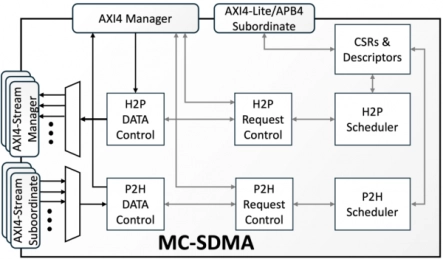

- The MC-SDMA IP core implements a highly configurable, bandwidth-efficient, and easy-to-use Direct Memory Access (DMA) controller that transfers data between the host system’s memory and multiple peripherals equipped with streaming interfaces.

- The core interfaces with the host memory via a manager AMBA® AXI4 (memory-mapped) port and provides access to its configuration and status registers (CSRs) via a subordinate AXI4-Lite or APB4 interface.

-

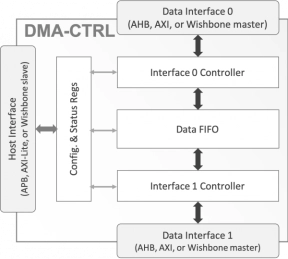

AHB/AXI/Wishbone DMA Controller

- The AXI4-SGDMA IP core implements a Host-to-Peripheral (H2P), or a Peripheral-to-Host (P2H) Direct Memory Access (DMA) engine, which interfaces the host system with an AXI4 Memory-Mapped master port and the peripheral with either a slave or a master AXI4-Stream port.

- The core operates in either Scatter-Gather (SG) Mode, reading descriptors from a run-time defined memory mapped-location, or in Direct Mode, transferring data according to a descriptor stored in local registers.

-

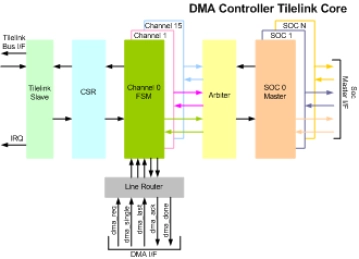

DMA Controller with TileLink IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Compliant with TileLink specification v1.7.1

- Supports access for Ring and Chained Descriptor Structures

- Configurable Transmit and Receive Engine based on Host Memory Data Width

-

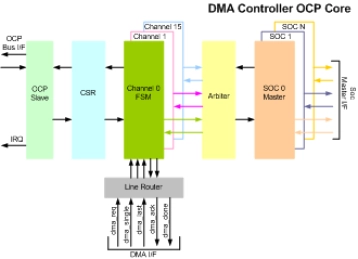

DMA Controller with OCP IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Compliant with OCP 3.1 specification

- Supports access for Ring and Chained Descriptor Structures

- Configurable Transmit and Receive Engine based on Host Memory Data Width

-

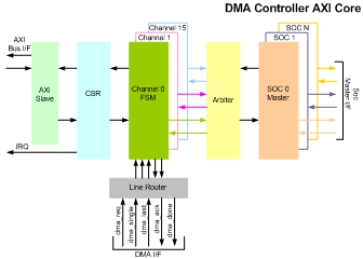

DMA Controller with AXI IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Supports latest ARM AMBA 3/4 AXI, AXI4-Lite, AMBA4 ACE, AMBA4 ACE-Lite, AXI4-Stream specification.

- Supports access for Ring and Chained Descriptor Structures

- Configurable Transmit and Receive Engine based on Host Memory Data Width

-

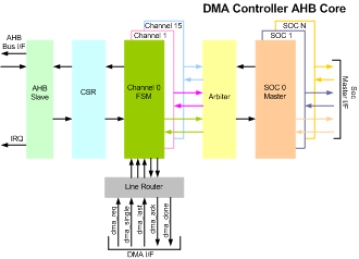

DMA Controller with AHB IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Compliant with ARM AMBA 2 AHB Specification

- Optional support for AMBA 3 AHB-Lite and AMBA 5 AHB Specification

- Supports access for Ring and Chained Descriptor Structures

-

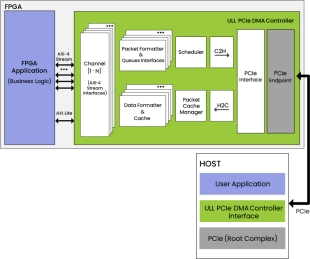

ULL PCIe DMA Controller

- The ULL PCIe DMA Controller is a high-performance, bidirectional data transfer solution. It is designed for seamless communication between FPGAs and host CPUs over PCIe.

- With a round-trip time as low as 585ns*, this IP core empowers developers to maximize resource utilization and achieve ultra-low latency without compromising performance.

-

Direct memory access (DMA) controller

- Tiny Heterogenous Processing

- System-wide Security

- Highly Configurable Feature Set

-

AHB Scatter-Gather DMA Controller

- Memory-based, linked-list transfer descriptors.

- 3 descriptor sizes to balance functionality and setup overhead.

- Configurable number of channels.

- Configurable number of peripherals (up to 64).