AnalogX IP

Filter

Compare

3,343

IP

from

145

vendors

(1

-

10)

-

Analog I/O Library with a custom 12V ESD Solution IN GF 55nm

- This I/O library is a silicon-proven, flip-chip-optimized analog and mixed-signal I/O Library for GlobalFoundries 55nm BCD technology.

- It provides a comprehensive set of 1.8V, 3.3V, 5V, and 12V analog I/O and power pads, designed for robust ESD protection, flexible pad-ring construction, and reliable operation across industrial temperature ranges.

-

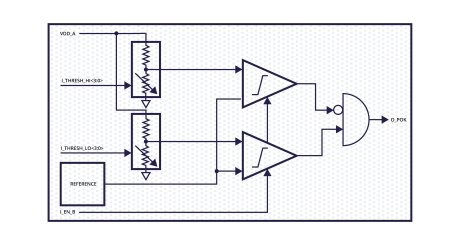

Power-OK Monitor

- The agilePOK is a Power OK monitor that consists of a voltage reference and comparators to set a programmable high and low threshold level for power supply integrity detection.

- The number of trigger outputs can be customized and each threshold can be adjusted during operation to support DVFS operation.

- This monitor can be used to detect loss of power or attacks to the power supply.

-

Ring oscillator-based analog PLL

- Our ring oscillator-based analog PLL provides good phase noise performance with extremely low energy consumption and small area compared to the state-of-the-art products.

- The programmable divider allows to shift the output frequency with a large locking range.

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

RTC Analog IP, Include 32K XOSC, Capaless LDO, POR, VDT - SMIC 40nm

- RTC Analog IP, Include 32K XOSC, Capaless LDO, POR, VDT

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 7nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 22nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;