ASIL IP

Filter

Compare

634

IP

from

30

vendors

(1

-

10)

-

ASIL B / ISO 26262 and ISO 21434 Compliant 1G-25G MACsec Security Module

- Synopsys MACsec Security Modules use scalable AES-GCM cryptography to provide confidentiality, integrity, authentication, and replay protection for Ethernet traffic.

- These modules integrate seamlessly with Synopsys Ethernet MAC & PCS IP, supporting high data rates with low latency. By incorporating Synopsys MACsec Security Modules into Ethernet IP solutions, networking SoC designers can ensure end-to-end security for data in motion between Ethernet-connected devices.

-

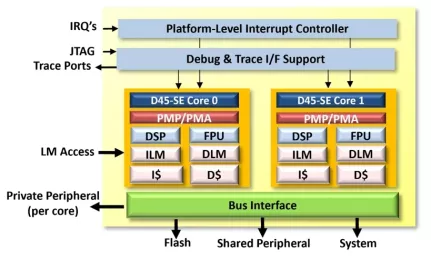

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

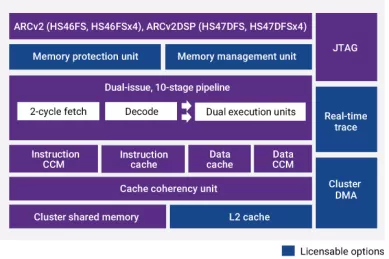

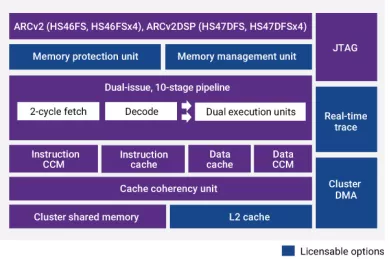

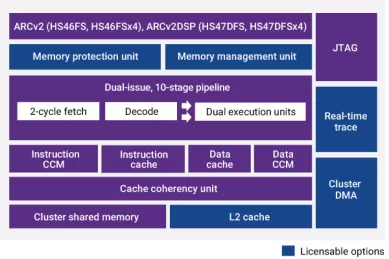

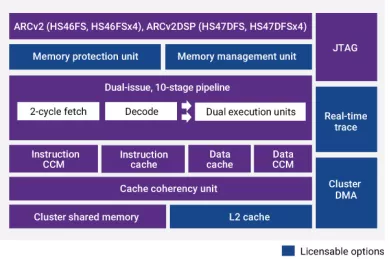

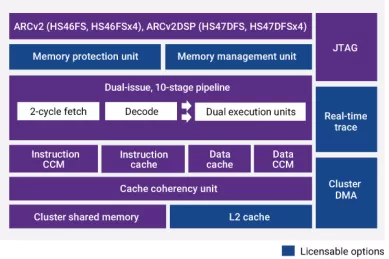

ARC HS48FSx4 quad-core, host processor , ASIL B / ASIL D support, incl. lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS48FS, host processor, with ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

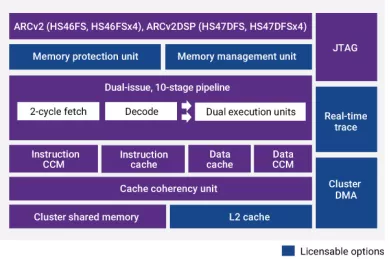

ARC HS47DFSx4 quad-core, w/ DSP extensions, ASIL B / ASIL D support, incl. lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS47DFS, with DSP extensions, and ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS46FSx4 quad-core with ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

ARC HS46FS with ASIL B / ASIL D support, including lock-step for functional safety applications

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Certified for ISO 262626 safety and ISO/SAE 21434 cybersecurity compliance

- Single solution for Automotive Safety Integrity Level B, C and D (ASIL B, C, D); Supports both ASIL D lockstep operation or ASIL B, C single core operation

- Includes hardware safety features: ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

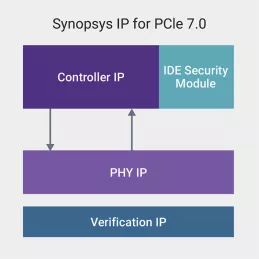

ASIL B Compliant PCIe 5.0 Integrity and Data Encryption Security Module (select configurations)

- Compliant with PCI Express IDE specification

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP packet-based interface

- Automotive compliant (ASIL B) aligning with ISO 26262 and ISO/SAE 21434

-

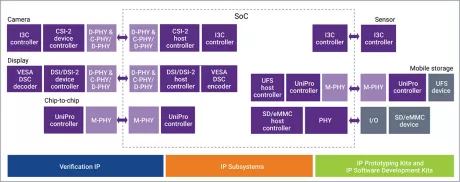

MIPI DSI-2 V2 Host Controller ASIL Compliant

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1