AMBA AHB PCI Express Bridge IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

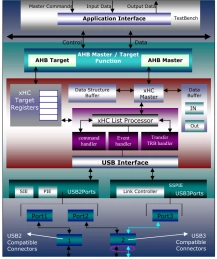

Super Speed USB 3.0 Extensible Host Controller xHCI

- The Super-Speed USB Host Controller is designed for flexibility, ease of use and provides ASIC/FPGA designers to implement a complete USB3.0 Host for 5 Gbps operation.

- The Host packet traffic can be explicitly routed and need not be broadcasted.