AES XTS IP

Filter

Compare

45

IP

from

17

vendors

(1

-

10)

-

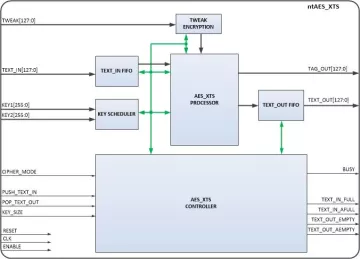

XTS mode AES Processor

- Supports high throughput AES XTS mode for data storage applications.

- Compliant with IEEE 1619-2007and NIST SP800-38E recommendations.

-

AES Core XTS

- Complies with IEEE 1619-2007 and NIST SP800-38E standards

- Performance selectable to meet or exceed USB 3.0 and SATA 3.0 (6 Gbps), even on low cost FPGA families

- Low area, implementation of AES-XTS suitable for data storage applications.

- Based on the NIST validated (Cert #953) AES-G3 implementation of FIPS 197 (November 2001) Advanced Encryption Standard

-

AES Encryption Core with XTS

- Full Verilog core

- 128 or 256 bit selectable AES encryption

- The AES-XTS algorithm is FIPS-197 certified, cert. no 2408.

- The encode and decode channels are made to look and act like independent FIFOs for ease of integration. The control block has a register interface to be easily managed by a hardware state machine or controlled by a processor for operations such as key initialization, and TWEAK configuration and management.

-

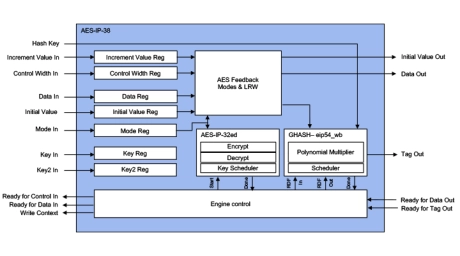

AES XTS/GCM Accelerators

- Wide bus interface

- Basic AES encrypt and decrypt operations

- Key sizes: 128, 192 and 256 bits

- Key scheduling in hardware, allowing key, key size and direction changes every 13/15/17 clocks with zero impact on throughput

- Hardware reverse (decrypt) key generation

-

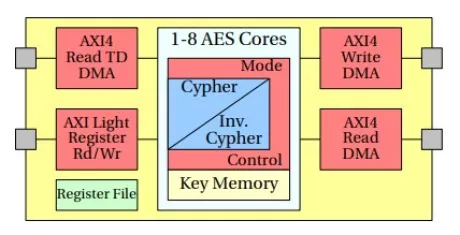

AES supporting ECB, CBC and XTS/XEX modes. Includes DMA and AXI interface.

- 100% AES compatible

- >2.4 GB/sec max throughput

- Up to 8 engines in parallel (configurable)

- Supports ECB, CBC and XTS/XEX modes

- Supports BitLocker acceleration

- Supports Encryption and Decryption

-

AES-SX-ULP-full Secure Core - High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - High-Performance/Ultra Low Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-GCM-XTS-up Secure Core - AES Encryption Core with Extreme SCA Protection for Ultra-High-Security Applications

- The Ultra-Secure AES IP core is designed for applications where maximum resistance to side-channel attacks (SCA) is paramount, even beyond certification-grade requirements.

- Supporting AES-128/256 encryption in ECB, CBC, CTR, GCM, and XTS modes, the core is built for environments where redundancy in protection is a feature, not a cost.

-

Cryptographic co-processor for lightweight cryptography

- Support AES-XTS mode — IEEE Std 1619-2007 standard compliance

- Support 128 and 256-bit key size

- Random memory block access support