AES IP

Filter

Compare

329

IP

from

68

vendors

(1

-

10)

-

AES-SX-ULP-full Secure Core - High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - High-Performance/Ultra Low Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - Ultra-Low-Power AES Core with Proven SCA Protection for Constrained Devices

- Ultra-Low-Power AES Core with Proven SCA Protection for Constrained Devices

-

AES-SX-GCM-XTS-up Secure Core - AES Encryption Core with Extreme SCA Protection for Ultra-High-Security Applications

- The Ultra-Secure AES IP core is designed for applications where maximum resistance to side-channel attacks (SCA) is paramount, even beyond certification-grade requirements.

- Supporting AES-128/256 encryption in ECB, CBC, CTR, GCM, and XTS modes, the core is built for environments where redundancy in protection is a feature, not a cost.

-

Cryptographic engine using the DES, Triple-DES or AES

- The cryptographic processor (CRYP) can be used both to encrypt and decrypt data using the DES, Triple-DES, AES or SM4 algorithms.

-

Stealth AES Encryption IP

- The Stealth AES Encryption IP provides advanced encryption capabilities to secure data transmission and storage in various applications, including IoT devices, edge computing systems, cloud platforms, and communication networks.

- Built on the Advanced Encryption Standard (AES), our IP offers robust encryption algorithms to safeguard sensitive information against unauthorized access and data breaches.

-

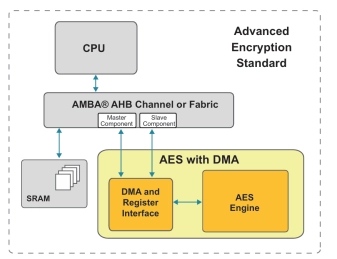

AHB AES with DMA

- The Advanced Encryption Standard (AES) IP Core is a complete hardware implementation encryption/decryption algorithm described in the U.S. Government Federal Information Processing Standards Publication 197 (FIPS 197).

- The AES IP Core implements the Rijndael algorithm which is a symmetric block cipher that can process 128-bit data blocks using 128, 192, or 256-bit cipher keys.

-

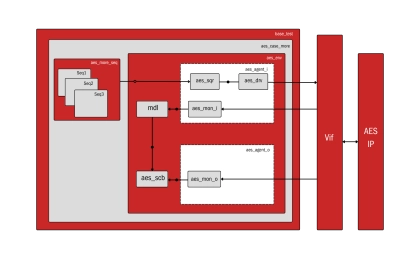

AES - Encrypts sensitive data to ensure secure communication and transactions

- AES (Advanced Encryption Standard) is a widely-used encryption algorithm designed to secure sensitive data. It offers high levels of security with key sizes of 128, 192, or 256 bits and supports multiple encryption modes, ensuring robust protection for communications and transactions.

- AES is implemented in Verification IP (VIP) to verify cryptographic hardware modules in systems such as processors and communication devices. Its versatility makes it crucial for applications ranging from government communications to cloud storage and financial transactions

-

AES GCM IP Core

- supports encryption and decryption

- supports offline and online key schedule

- supports 128, 192 and 256-bit key lengths

- has masked and non-masked modes

- supports encryption and decryption