ADAS IP

Filter

Compare

191

IP

from

28

vendors

(1

-

10)

-

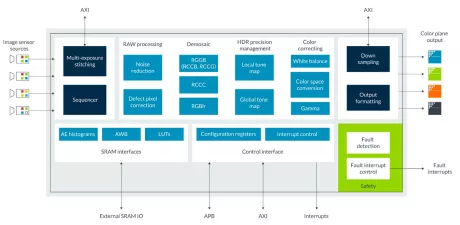

Image Signal Processing for ADAS and Display Applications

- Multi-Camera Support

- Advanced Image Processing

- Every Pixel Reliable

-

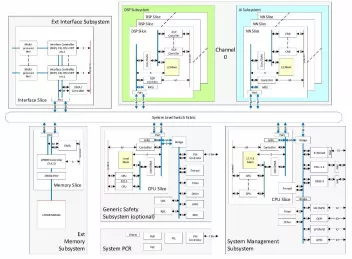

Single channel ADAS chip with FuSa monitor

- The SFA 250A has been designed to be easy to adapt to suit the support needs of the customer’s IP as it is scalable, both in terms of function and performance, as well as modular as multiple versions can be combined to form larger solutions.

-

-

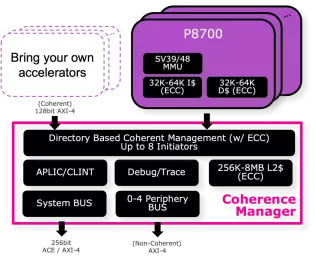

Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

- The only Multi-Threaded Out-of-Order RISC-V Core with ASIL-B Certification

- Highly scalable multi-core, multi-cluster, coherent computing solution

- MIPS extensions for improved performance and functionality

- Use in Automotive, Datacenter, and Embedded applications

-

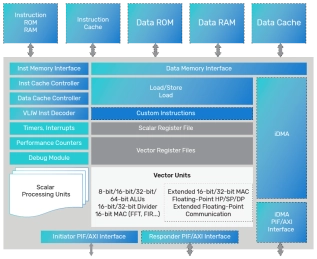

Tensilica ConnX 120 DSP

- Certified ISO 26262:2018 ASIL-compliant

- VLIW parallelism issuing multiple concurrent operations per cycle

- 256-bit SIMD

- Up to 64 MAC

-

Functional-Safety & Secure LPDDR3 Memory Subsystem

- Safe & Secure-LPDDR3 that is ready for ASIL (Automotive Safety Integrity Level) and secure by design

- Functional Safety out-of-the box design, with an extensive ASIL documentation package.

- Integrated security features into the controller. Characterized for extended operating conditions and long-term reliability.

-

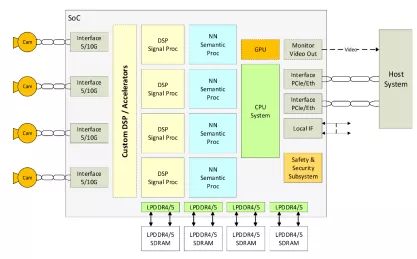

Safety Enhanced GPNPU Processor IP

- A True SDV Solution

- Fully programmable – ideal for long product life cycles

- Scalable multicore solutions up to 864 TOPS

- Solutions for ADAS, IVI and ECU products

-

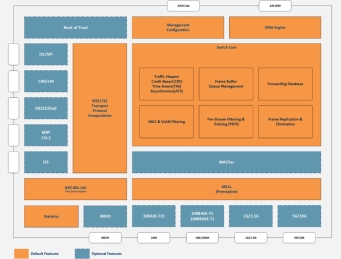

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

SENT Protocol IP Core for Automotive Communication

- The DSENT, a hardware implementation of the Single Edge Nibble Transmission (SENT) protocol controller.

- Designed to comply with the SAE-J2716 standard, DSENT delivers a robust, low-cost solution for reliable data communication between automotive sensors and central units such as Engine Control Units (ECUs).

-

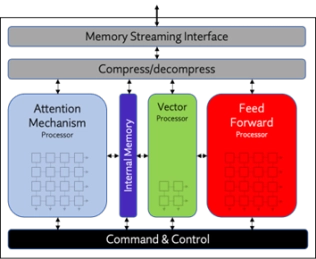

NPU IP Core for Automotive

- Origin Evolution™ for Automotive offers out-of-the-box compatibility with popular LLM and CNN networks. Attention-based processing optimization and advanced memory management ensure optimal AI performance across a variety of today’s standard and emerging neural networks.

- Featuring a hardware and software co-designed architecture, Origin Evolution for Automotive scales to 96 TFLOPS in a single core, with multi-core performance to PetaFLOPs.