7nm DSP SerDes IP

Filter

Compare

7

IP

from

3

vendors

(1

-

7)

-

1-56Gbps Serdes - 7nm (Multi-reference Clock)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Ultra Low Latency)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Area-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-112Gbps Serdes - 7nm

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (PPA-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

SerDes IP

- 10dB to 35dB bump-to-bump insertion loss

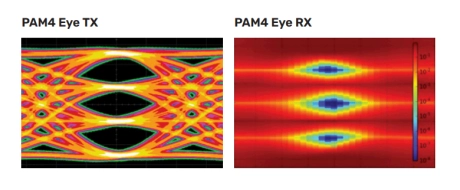

- Multi-rate support for 56Gbps to 112Gbps PAM4 and NRZ

- Integrated PLL

- Robust clock distribution architecture

- Advanced mixed signal analog equalization architecture

- Fully adaptive and programmable RX equalization

- Auto-negotiation

- Link Training

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs