5G Ethernet Subsystem IP

Filter

Compare

10

IP

from

3

vendors

(1

-

10)

-

USXGMII Subsystem

- Designed to meet the USXGMII specification EDCS-1467841 revision 1.4

- Supports 10M, 100M, 1G, 2.5G, 5G, or 10GE data rates over a 10.3125 Gb/s link

- Both media access control (MAC) and physical coding sublayer/physical medium attachment (PCS/PMA) functions are included

- Code replication/removal of lower rates onto the 10GE link

-

400G/800G High Speed Ethernet Controller PCS/FEC

- IEEE 802.3 compliant, UNH tested and ISO 26262 ASIL-B qualified

- Enhanced active functional safety features

-

10G to 400G High Speed Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

200G/400G High Speed Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

1G to 200G High Speed Channelized Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

10G to 400G High Speed Channelized Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

400G/800G High Speed Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

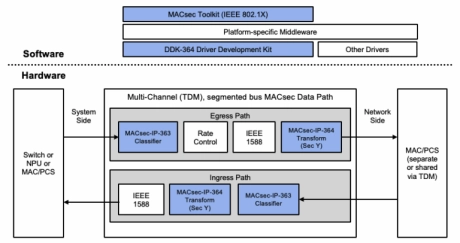

1.6T/3.2T Multi-Channel MACsec Engine with TDM Interface (MACsec-IP-364)

- The MACsec-IP-364 is a MACsec/IPsec engine developed specifically for high-speed, multi-rate and multi-port Ethernet devices.

- Its architecture provides an optimal multi-protocol solution for aggregate throughput for 1.6T and 3.2T.

- The MACsec-IP-364 is ideal for deployment in data center, enterprise and carrier network applications, as well as network-attached high-performance computing.

-

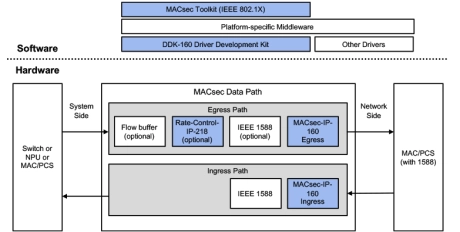

1G to 100G Single-Port MACsec Engine

- Complete HW/SW system.

- Driver Development Kit.

- High-speed MACsec Frame Engine

- Silicon-proven implementation

- Fast and easy to integrate into SoCs.

- Flexible layered design.