56G Ethernet PHY IP

Filter

Compare

5

IP

from

2

vendors

(1

-

5)

-

56G Ethernet PHY in TSMC (16nm, 12nm)

- Physical Coding Sublayer (PCS) block with PIPE interface

- Supports PCIe 6.0 (PAM-4), 5.0, 4.0, 3.1, 2.1, 1.1 encoding, backchannel initialization

- Supports x1, x2, x4, x8, and x16 hard macro configurations

- Lane margining at the receiver

-

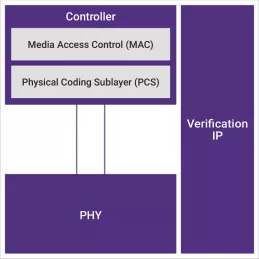

High Speed Ethernet Quad 10G to 100G PCS

- Compliant with the IEEE 802.3 standard

- Configurable IP available in single or quad port for speeds from 1G to 100G

- Designed to be used with Synopsys 100G Ethernet MAC IP for 100G Systems

- Integration tested with the Synopsys 100G Ethernet MAC IP and Synopsys 56G Ethernet PHY IP

-

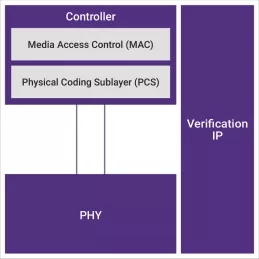

High Speed Ethernet Gen-2 Quad 100G PCS IP

- Compliant with the IEEE 802.3 standard

- Configurable IP available in single or quad port for speeds from 1G to 100G

- Designed to be used with Synopsys 100G Ethernet MAC IP for 100G Systems

- Integration tested with the Synopsys 100G Ethernet MAC IP and Synopsys 56G Ethernet PHY IP

-

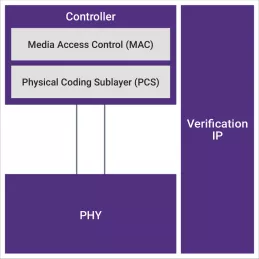

High Speed Ethernet 4/2/1-Lane 100G PCS

- Compliant with the IEEE 802.3 standard

- Configurable IP available in single or quad port for speeds from 1G to 100G

- Designed to be used with Synopsys 100G Ethernet MAC IP for 100G Systems

- Integration tested with the Synopsys 100G Ethernet MAC IP and Synopsys 56G Ethernet PHY IP

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C