4G LTE IP

Filter

Compare

11

IP

from

8

vendors

(1

-

10)

-

4G LTE/LTE-A Turbo Decoder

- Compliant with 3GPP Release 8 LTE turbo decoding

- Compliant with 3GPP Release 10 LTE Advanced turbo decoding

- Support for codeword CRC and up to four transport block CRCs

-

-

-

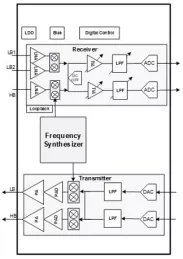

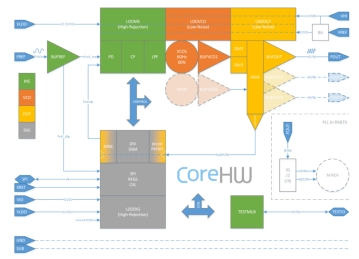

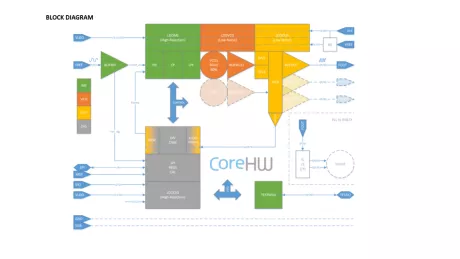

3rd Generation Software Defined Radio RF IP

- Frequency Range: 100MHz - 2.6GHz

- Bandwidth Range: 180KHz ~ 20MHz

- Supports HD-FDD/TDD modes.

- Low phase-noise Frac-N synthesizer

-

Software Defined Radio for high end 4G/ 5G and large MIMO application

- 8x8 Transmit and Receive Antennas support

- TI Multi-core communication processor, 1.2 GHz

- 8 C66X DSP cores and 4 ARM cores

- NOR flash – 32MB, NAND Flash – 512MB

-

LTE / HSPA turbo decoder

- - LTE rate matching : subblock deinterleaver, bit collection

- - HSPA rate-matching : E-DCH and HS-DSCH transport channels

- - HARQ combining

- Two performance profiles are available :

-

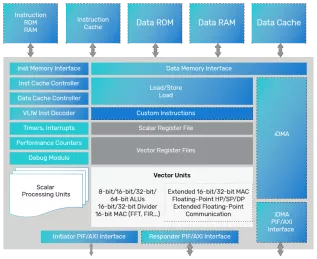

Tensilica ConnX 110/120

- Certified ISO 26262:2018 ASIL-compliant

- VLIW parallelism issuing multiple concurrent operations per cycle

- 128-bit or 256-bit SIMD

-

Dual WideBand Frequency Synthesizer with Integrated VCO and Loop Filter - GlobalFoundries 55nm

- PLL1 for LTE with VCO1

- PLL2 for LTE&GSM with VCO1 and VCO2

- Small size, high-performance and low-power (24mW)

- Various power and performance modes

- Power supply 1.35V and 1.8V

- Reference signal (FREF) from 10MHz to 400MHz

-

Dual WideBand Frequency Synthesizer with Integrated VCO and Loop Filter

- 3GPP superset LO sub-system (All bands + CA)

- PLL1 [0.49mm2] for LTE with VCO1

- PLL2 [0.76mm2] for LTE&GSM with VCO1 and VCO2

- Small size, high-performance and low-power (24mW)

-

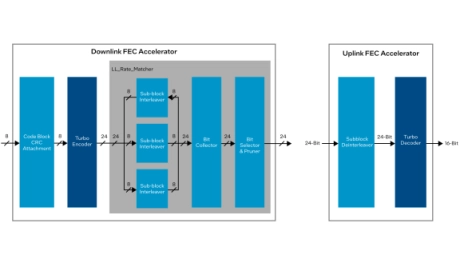

Turbo Intel® FPGA IP

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.