40nmULP Memory Compiler IP

Filter

Compare

3

IP

from

3

vendors

(1

-

3)

-

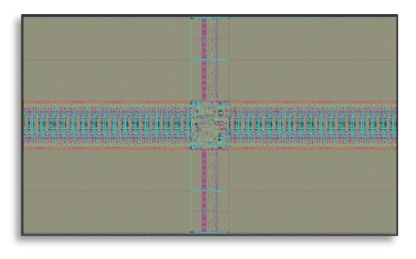

High Speed Single Port Compiler on TSMC 40nm ULP

- Low voltage

- Ultra low power data retention

- Self biasing

- Soft error immunity

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.