22nm SerDes IP

Filter

Compare

19

IP

from

6

vendors

(1

-

10)

-

PCIe 4/3/2 SerDes PHY - GLOBALFOUNDRIES 22nm

- Duplex lane configurations of x2, x4, and x35

- Transmit swing of at least 800mV differential peak-to-peak for MR & LR, 360mv for SR

- Support for AC-coupled interfaces

- Fine-grain power up/down capability for power optimization, and ability to turn off unused link(s)

-

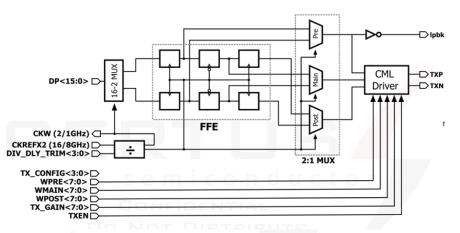

32Gbps SerDes PHY in GF 22nm

- This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs.

- The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation.

-

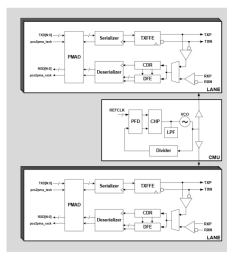

Ultra-Low Latency 32Gbps SerDes IP in TSMC 22nm ULP

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Ultra-low latency 2/4/8-bit parallel interface mode for lowest possible latency

-

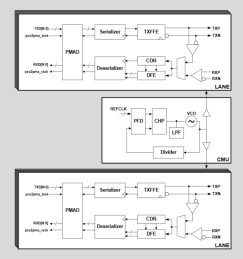

32Gbps SerDes IP in TSMC 22nm ULP

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Configurable low latency parallel data interface for optimal system performance

-

32G LR Multi-Protocol SerDes (MPS) PHY - GLOBALFOUNDRIES 22nm

- Supports data rates of 2.5 to 32 Gbps

- Optimized for low-power operation and north/south die-edge placement

- AC-coupled RX front end with on-chip capacitors

- Flexible ASIC interface for sharing impedance codes among multiple PMA hard macros and reducing the number of external reference resistors for impedance calibration

-

SerDes PHY IP in TSMC (7nm, 12/16nm, 22nm, 28nm)

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

TSMC CLN22ULLLVT 22nm Clock Generator PLL - 175MHz-875MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN22ULLLVT 22nm Clock Generator PLL - 350MHz-1750MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN22ULLLVT 22nm Clock Generator PLL - 700MHz-3500MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

TSMC CLN22ULL 22nm Clock Generator PLL - 125MHz-625MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.