Vendor:

T2M GmbH

Category:

USB

USB 3.1 Gen1 / Gen2 Device Controller IP

USB 3.1 Device controller is a configurable core and implements the USB 3.1 Device functionality that can be interfaced with thir…

Overview

USB 3.1 Device controller is a highly configurable core and implements the USB 3.1 Device functionality that can be interfaced with third party USB 3.1 PHY’s. USB3.1 Device controller core is part of USB3.0 family. This Device Controller core is architected with an high performance DMA engine based on USB3.1 specification.

This Controller core is carefully partitioned to support standard power management schemes which include extensive clock gating and multiple power wells for aggressive power savings required for mobile and handheld applications. This controller has a very simple application interface which can be easily adapted to standard on-chip-bus interfaces such as AXI, AHB, OCP as well as other standard off-chip interconnects making it easy to be integrated in a wide range of applications. The Controller also has a dedicated PHY Type-C connector Interface for identifying Type-C specific features such as cable orientation, ID function based on Configuration data channel etc.

This Controller core is carefully partitioned to support standard power management schemes which include extensive clock gating and multiple power wells for aggressive power savings required for mobile and handheld applications. This controller has a very simple application interface which can be easily adapted to standard on-chip-bus interfaces such as AXI, AHB, OCP as well as other standard off-chip interconnects making it easy to be integrated in a wide range of applications. The Controller also has a dedicated PHY Type-C connector Interface for identifying Type-C specific features such as cable orientation, ID function based on Configuration data channel etc.

Key features

- Compliant with USB3.1 Specification Rev1.0

- Implements Phy Logical/ Link / Protocol Layers.

- Supports Aggressive Low Power Management

- Configurable system clock frequency

- Support simultaneous Multiple IN transfers.

- Implements PTM.

- Supports Bulk Streaming.

- Configurable PIPE Interface: 8, 16, 32 bit.

- Flexible User Application Logic which includes Optional Support for EP0 Processer for processing control transfers

- Optional proprietary DMA Controller in Application Layer.

- Optional support for Type-C connectors

- Supports Type2 Header Buffers

- Supports SCD/LBPM LFPS Messages

- Simple Register Interface for internal Register Access.

- Support for various Hardware and Software Configurability regarding Core characteristics.

- Support Data, Video and Switch

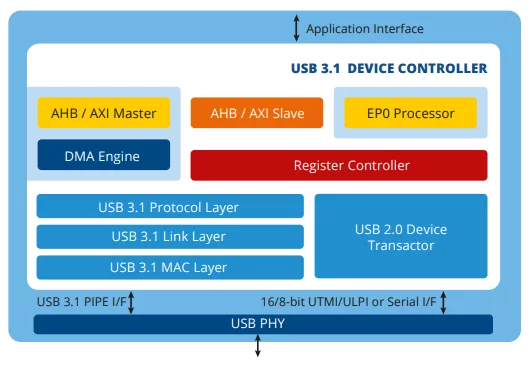

Block Diagram

USB 3.1 Device Controller IP block diagram

Benefits

- Highly modular and configurable design

- Layered architecture

- Fully synchronous design

- Supports both sync and async reset

- Clearly demarked clock domains

- Extensive clock gating support

- Multiple Power Well Support

- Software control for key features

Applications

- Automotive

- Smartphones

- Tablets

- Notebooks

- Gaming

- Digital cameras and camcorders

- Storage

- Wireless communication

- Set-top boxes

- Smart TVs and digital TVs

- Chip-to-chip low-power interconnects

What’s Included?

- Configurable RTL code

- HDL-based test bench and behavioral models

- Test cases

- Protocol checkers, bus watchers, and performance monitors

- Configurable synthesis shell

- Design guide

- Verification guide

- Synthesis guide

- FPGA platform for pre-tape-out validation

- Reference firmware

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

USB 3.1 Device Controller IP

Vendor

T2M GmbH

Provider

T2M GmbH

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

In addition to performance and interoperability, achieving low power has been one of the requirements for industry standards specifications. Some of the key specifications like Universal Serial Bus (USB), PCI Express (PCIe), and MIPI have defined power saving features for burst traffic. This whitepaper explains how Synopsys USB IP offers low power using various low power states that go beyond the basic features.

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

Gervais Fong, Synopsys

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Sharmion Kerley, MIPI Alliance

Frequently asked questions about USB IP cores

What is USB 3.1 Gen1 / Gen2 Device Controller IP?

USB 3.1 Gen1 / Gen2 Device Controller IP is a USB IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.