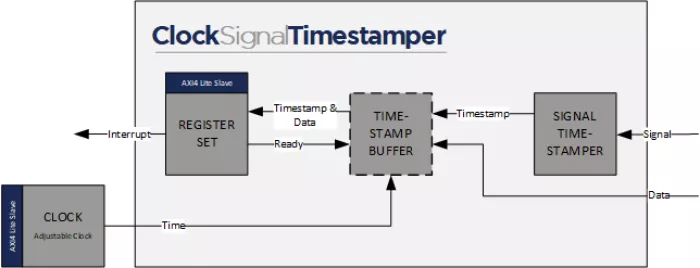

The Signal Timestamper from NetTimeLogic is a timestamper with nanosecond resolution (second and nanosecond format). It uses NetTimeLogic's Adjustable Clock core as source for timestamping. Together with the event to timestamp, data can be provided which will then be latched, so that the timestamp and data can be aligned with each other. Timestamps will generate an IRQ and timestamps can optionally be buffered for burst handling.

The IP core comes with a Linux Driver

Time aligned Signal Timestamper core

Overview

Key Features

- Signal edge timestamping

- 32 bit second and 32 bit nanosecond timestamp

- Optional timestamp buffer for burst handling

- Configurable polarity

- Input delay compensation

- Data snapshot for timestamp alignment

- Interrupt generation

- Interrupt masking

- Edge counter for event detection

- Maximum event rate depends on CPU and AXI bus load

- AXI4 Light register set or static configuration

- Timestamp resolution with 50 MHz system clock: 10ns

- Linux driver

Benefits

- Coprocessor handling signal timestamper based on a reference time standalone in the core.

- Simple interface

Block Diagram

Applications

- Distributed data acquisition

- Ethernet based automation networks

- Automation

- Robotic

- Automotive

- Test and measurement

Deliverables

- Source Code (not encrypted, not obfuscated)

- Reference Designs

- Testbench with Stimulifiles

- Configuration Tool

- Linux Driver

- Documentation

Technical Specifications

Short description

Time aligned Signal Timestamper core

Vendor

Vendor Name

Availability

Now

Related IPs

- Time aligned Signal Generator core

- Time aligned Frequency Generator core

- Centralised Real Time Processor IP Core

- 256x16 Bits OTP (One-Time Programmable) IP, 256x16 Bits One Time Programmable Device SMIC 110nm 1.2V/3.3V Mixed Signal Generic Process

- Multi-rate Audio 24-Bit DAC/PLL Core

- 3-D Audio Processing Core