1G TCP Offload Engine TOE Very Low Latency (TOE)

INT 1011 is flexible that is customizable for layer-3, layer-4, layer-5 network infrastructure and network security systems appli…

Overview

INT 1011 is highly flexible that is customizable for layer-3, layer-4, layer-5 network infrastructure and network security systems applications. It is recommended for use in, among others, high performance Servers, NICs, SAN/NAS and data center applications. It provides the key IP building block for a single high performance Giga bit Ethernet ASIC/ASSP/FPGA.

INT 1011 provides capability for enterprises to differentiate their Network security and Network infrastructure appliances from others

INT 1011 can process TCP/IP, for in-line network security appliances, sessions in both directions, simultaneously, at full G-bit rate. This relieves the host CPU from costly TCP/IP buffer stack execution and maintenance tasks.

INT 1011 can process TCP/IP sessions and has the capability to process other relevant protocols such as FTP, UDP, ICMP, TFTP etc on all inbound as well as outbound traffic simultaneously without compromising performance at sustained Gigabit speeds.

Key features

- Ideal for high performance and mid performance specialized, differentiable ASICs or FPGAs for Network security or Network infrastructure applications

- Less than 4000 Xilinx slices, Altera ALMs or 150,000 ASIC gates + on-chip memory

- Fully integrated 100 M bit/1-G bit high performance EMAC.

- Scalable MAC Rx FIFOs and Tx FIFOs make it ideal for optimizing system performance.

- Hardware implementation of TCP/IP stacks’ control plane and data plane.

- Hardware implementation of ARP protocol. ARP table creation, deletion, management (optional)

- Customizable for IP-protocol only.

- Capture, filter, store and monitor TCP-Ports (optional)

- Capture, filter, store and monitor IP all addresses (opt)

- On-chip DDR or SSRAM memory controller which can address from 4K Bytes to 4 MB Bytes on chip or 256 MB off chip memories (User customizable, optional)

- User FIFO interface for application data storage

- Many trade-offs for some functions performed in hardware or software

- Configurable Packet buffers, session table buffers On-chip or Off-chip memories, attached DDR I/II interface. Depending on system, performance, ASIC/FPGA size requirements-> User Customizable, (optional)

- Interfaces directly to GMII, RGMII, MII external 10/100/ 1000 Mbit Phy interfaces

- Architecture can be scaled up to 10-G bits

- Customizable to handle jumbo frames

- AMBA 2.0 bus interface for Local Processor control. PPC, MIPS and other CPU interfaces available

- User programmable/ prioritize-able interrupts

- Performs all connection/ session management tasks

- Monitors, Stores, Maintains and processes more than 4024 live TCP sessions. Customizable, depending upon on-chip memory availability.

- Extendable to 64K TCP sessions. Internal Memory dependent.

- Wire-speed 2-Gbps performance at full duplex

- Can be expanded to process up to 64K connections per sec.

- TCP + IP check sum generation and check performed in hardware in less than 6 clks (30 ns at 200 MHz) vs 1-2 us by typical software TCP-stack

- Connection set up and tear down/termination

- User programmable Session table parameters

- Dedicated set of hardware Timers for each TCP/IP session or customizable for sharing stale sessions.

- Multiple ‘slot storage’ for fragmented packets. More slots allocated when more On-chip Memory available. Self-checking available memory logic. (optional)

- Out of sequence packet detection/storage and Reassembly/Segmentation (optional)

- RDMA- Direct Data placement in Applications buffer at full wire speed without CPU-> reduces CPU’s buffer copy time and utilization by 95%

- Future Proof- Flexible implementation of TCP Offload

- Accommodates future Specifications changes.

- Basic mini API available for PPC architecture. Others OSs/CPUs also available

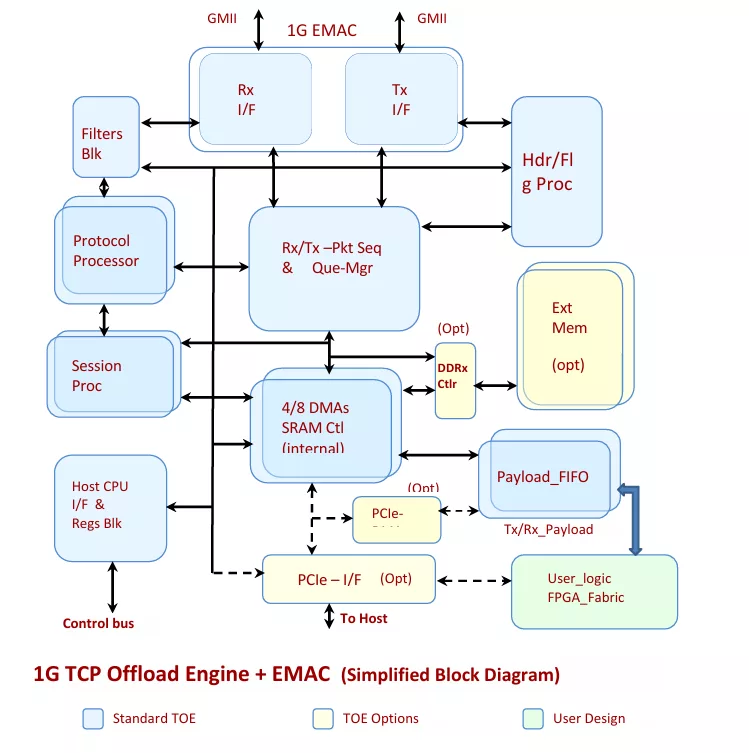

Block Diagram

Benefits

- Increase TCP/IP performance by 10 X

- Increases network traffic bandwidth by 10 X

- Improves network efficiency significantly

- Only TCP/IP hardware engine SOC with these features.

- Tested in IDS/IPS appliance.

What’s Included?

- Verilog source code or NetList.

- Verilog models for various components e.g. TCP/IP (transaction model) EMAC, memory interface etc.

- TCP Model

- Verification suite

- Test packet-traffic suite

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is 1G TCP Offload Engine TOE Very Low Latency (TOE)?

1G TCP Offload Engine TOE Very Low Latency (TOE) is a Ethernet IP core from Intilop Corp. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.