Tamper-resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M

For embedded developers seeking to hinder physical tampering and achieve a higher level of security certification, Arm offers the…

Overview

For embedded developers seeking to hinder physical tampering and achieve a higher level of security certification, Arm offers the Cortex-M35P: a robust, high-performing processor. It builds upon the proven Arm Cortex-M technology deployed in billions of SoCs, making physical and software security accessible for all developers.

Physical security is generally complex – however, the ease-of-use of the Cortex-M35P processor, combined with the support of Arm and the Arm ecosystem, now open the door for embedded developers to deliver many new devices with physical resilience at the heart.

Key features

- Architecture: Armv8-M Mainline (Harvard)

- ISA Support: Thumb/Thumb-2

- Pipeline: Three-stage

- Software security: Optional TrustZone for Armv8-M, stack pointers checking

- Physical security: Built-in protection from invasive and non-invasive attacks

- DSP Extensions

- Optional DSP/SIMD instructions

- Single cycle 16/32-bit MAC

- Single cycle dual 16-bit MAC

- 8/16-bit SIMD arithmetic

- Floating Point Unit

- Optional single precision floating point unit

- IEEE 754 compliant

- Co-processor interface: Optional dedicated co-processor bus interface for up to 8 co-processor units for custom compute

- Memory Protection: Optional Memory Protection Unit (MPU) with up to 16 regions per security state

- Interrupts: Non-Maskable Interrupt (NMI) and up to 480 physical interrupts with 8 to 256 priority levels

- Wake-up Interrupt Controller: Optional for waking up the processor from state retention power gating or when all clocks are stopped

- Sleep Modes: Integrated Wait for Event (WFE) and Wait for Interrupt (WFI) instructions with Sleep On Exit functionality

- Debug: Optional JTAG and Serial Wire Debug ports. Up to 8 Breakpoints and 4 Watchpoints

- Trace: Optional Instruction Trace (ETM), Micro Trace Buffer (MTB), Data Trace (DWT), and Instrumentation Trace (ITM)

- Cache: Instruction cache

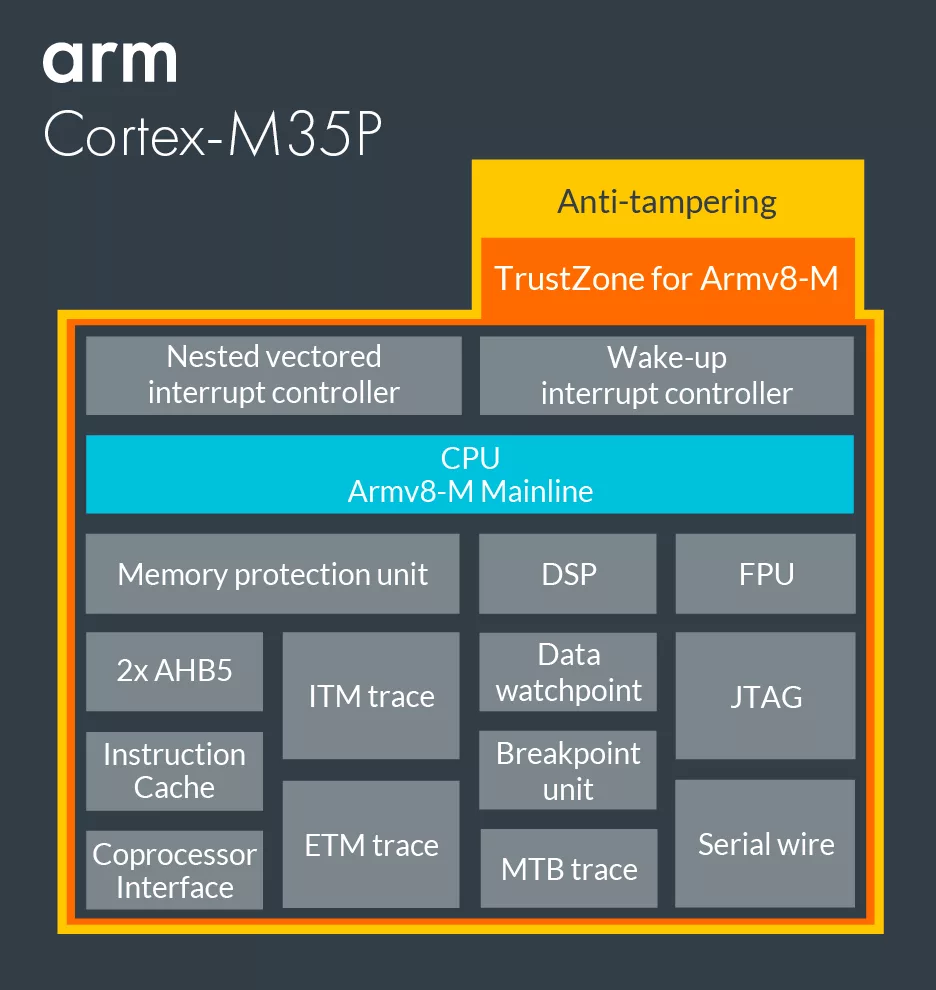

Block Diagram

Benefits

- Cortex-M35P extends the anti-tampering features of the SecurCore family of processors, making this state-of-the art technology available to Cortex-M developers. Robust embedded security is more accessible than ever with the benefits of both physical and software security, using the optional TrustZone isolation.

Applications

- Payment

- Integrated or Embedded Secure Elements

- Secure embedded applications

- IoT

- Industrial

- Automotive

- Healthcare

- Medical

- Biometric data

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Tamper-resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M?

Tamper-resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M is a CPU IP core from Arm Ltd. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.