The SPD5 Hub function controller IP has been developed to interface I3C/I2C Host Bus and it allows an isolation of local devices like Temperature Sensor(TS), from master host bus. This SPD5 has Two wire serial interface like SCL, SDA.

SPD5118 Hub Controller IP

Overview

Key Features

- Compliance as per JEDEC’s JESD300-5B

- Upto 12.5MHz speed supported

- Bus Reset

- SDA arbitration

- Parity Check is enabled

- Packet Error Check is supported (PEC)

- Supported Switch from I2C to I3C Basic Mode and vise versa

- Default Read address pointer Mode supported

- Support SPD5 Hub write and read operations with or without PEC enabled

- In-band Interrupt (IBI)

- Support Write Protection for each block of NVM memory

- Interrupt Arbitration

- Among SPD5 Hub Devices

- Among Local Target Devices behind one SPD5 Hub Devices

- Between SPD5 Hub Device and Local Target Devices Behind the Hub

- Among Local Target Devices behind Different SPD5 Hub Devices

- Between Host and Any SPD5 Hub or Any Local Target Devices Behind Hub

- Clearing Device Status and IBI Status Registers

- Packet Error Check & Parity Error Handling

- CCC Packet Error Handling

- I3C Basic Common Command Codes (CCC)

- ENEC

- DISEC

- RSTDAA

- SETAASA

- GETSTATUS

- DEVCAP

- SETHID

- DEVCTRL

- Dynamic IO Operation Mode Switching

- Bus Clear and Bus Rest

- SPD5 Command

- NVM memory

- W1M, R1M

- W2M, R2M

- W4M, R4M

- W16M, R16M

- Register Space

- W1R, R1R

- W2R, R2R

- W4R, R4R

- W16R, R16R

- NVM memory

- NVM memory Write and Read access

- Offline Tester operation is supported

Benefits

- Time to Market and Easy to integrated in your SoC

- Compliance as per JEDEC specification

- Silicon Proven

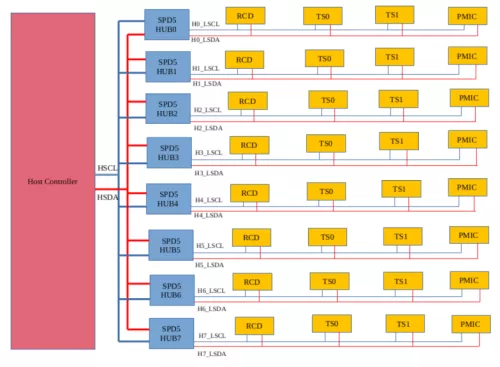

Block Diagram

Video

SPD5 FPGA TESTING (I3C Master to I2C Device GY-63 through SPD5 HUB)

DATA READ FROM GY-63 The SPD5 Hub Function IP has been developed to interface I3C/I2C Host Bus and it allows an isolation of local devices like Temperature Sensor(TS), from master host bus. This SPD5 has Two wire serial interface like SCL, SDA.

Applications

- DDR5 DIMM application Environment

- Power Management Application

- DDR5 NVDIMM application

- Customer Electronics

- Memory Devices

- Automotive Devices

Deliverables

- Verilog Source code.

- User Guide.

- IP Integration Guide.

- Run and Synthesis script.

- Encrypted Verification Testbench Environment.

- Basic Testsuite.

Technical Specifications

Maturity

Silicon Proven at Multiple customer SPD hub IC

Availability

immediate