Learn more about Power On Reset (POR) IP core

In the boot process various modules/peripherals (like clock controller or security handing module and other master/slaves) initialized as per the SoC architecture and customer applications. In Multi core SoCs, first primary core (also called booting core) start up in boot process and then secondary cores are enabled by software.

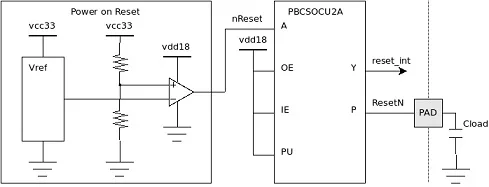

Reset is necessary to initialize the system and reach to a known state. Just like multiple clocks are required in an SoC to sustain various use models and performance, multiple resets are designed to cater different functional requirements. With this advent we also invite some issues due to crossings among different reset domains. In a sequential design, if the reset of source register is different from the reset of destination register even though the data path is in same clock domain, this will become asynchronous crossing path and can cause metastability at destination register.

VLSI design teams are eagerly anticipating the full functional fab out Silicon to portray their months of hard work, on the other hand the Test teams are busy planning their functional coverage (to fill in the gaps of scan (atpg) patterns coverage holes) but more often than not, the unexpected happens and the teams are busy debugging the Si bring up for functional cases. This paper is trying to highlight the seemingly innocuous issues that occur on first few day of Si bring up and proactive steps that would help reduce these cycle.

With the increase complexity of modern day SoCs, the number of memory blocks and LBIST partitions are increasing, which is in turn making the verification efforts quite challenging. This paper highlights the key points to keep in mind while deciding the verification strategy for self-test, and what are the road-blocks in executing this “ideal” verification plan.

Reusable Verification Infrastructure for A Processor Platform to deliver fast SOC development

In a current trend of SoC Design, IC’s are becoming more and more complex so the challenges of meeting all the design requirements have become increasingly difficult.