Simulation VIP for MIPI CSI-2

Cadence's best-in-class Verification IP (VIP) for MIPI® CSI-2sm for IP, SoCs and, system-level design testing.

Overview

Cadence's best-in-class Verification IP (VIP) for MIPI® CSI-2sm for IP, SoCs and, system-level design testing.

In production since 2008 on dozens of production designs.

Cadence provides a mature and comprehensive VIP for the CSI-2 protocol, which is part of the MIPI family. Incorporating the latest protocol updates, the Cadence® VIP for CSI-2 provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for CSI-2 helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported specification: MIPI CSI2 v1.3, v2.0, v2.1, v3.0, v4.0, MIPI D-PHY v1.2, v2.1, v2.5, MIPI C-PHY v1.0, v1.2, v2.0, MIPI CSE v1.0, MIPI PAL/CSI2 v1.0, and MIPI A-PHY v1.0.

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

|

Feature Name |

Description |

|---|---|

|

PHY Interfaces |

|

|

PPI Data Bus Width |

|

|

Data Lanes |

|

|

Data Types |

|

|

Clock |

|

|

Interleaving |

|

|

Virtual Channel Extension |

|

|

Ultra-Low Power Mode (ULPM) |

|

|

Triggers |

|

|

Pixel Layer |

|

|

Scrambling |

|

|

Latency Reduction Transport Efficiency (LRTE) |

|

|

Efficient Packet Delimiter (EPD) |

|

|

Alternate Calibration Sequence for D-PHY |

|

|

Frame Synchronization Packets |

|

|

Spacer Byte Generation |

|

|

End of Transmission packet (EoTp) |

|

|

Spacers Generation |

|

|

Smart Region of Interest |

|

|

Unified Serial Link |

|

|

CSI-2 Over DPHY v2.5 |

|

|

CSI-2 Over CPHY v2.0 |

|

|

CSI2 over A-PHY v1.0 |

|

|

Camera Service Extension (CSE) |

|

|

Protocol Adaptation Layer (PAL) |

|

| CSE v2.0 FSED |

|

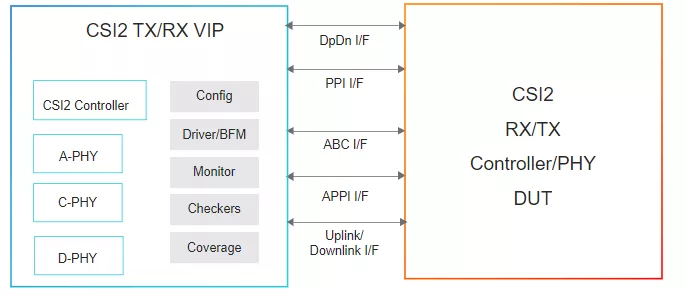

Block Diagram

Benefits

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

- Packet tracker creation for easy debugging

- Dynamic activation to enable setting the VIP as active/passive during run time

- Provides extensive coverage in e and SystemVerilog

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is Simulation VIP for MIPI CSI-2?

Simulation VIP for MIPI CSI-2 is a MIPI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.