Overview

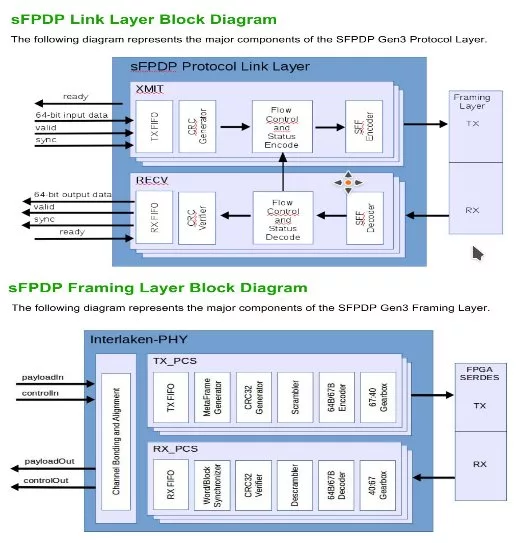

Serial Front Panel Data Port Gen3 is a next-generation, high bandwidth serial communications protocol defined by the ANSI/VITA 17.3-2018 standard. sFPDP-Gen3 supports single-lane or multi-lane links with automatic channel bonding and uses a 64B/67B framing layer to achieve over 95% bandwidth efficiency. sFPDP-Gen3 supports the same user data frame types found in the previous VITA 17.1 specification, allowing for easy system upgrades. Serial FPDP Gen3 is ideal for use in applications such as high-speed communication system backplanes, high-bandwidth remote sensor systems, signal processing, data recording, and highbandwidth video systems. sFPDP can be used in point-to-point or loop topologies, uni-directional or bidirectional links, and easily supports different types of data with efficient and flexible data framing options.

StreamDSP is committed to performance, efficiency, and flexibility. Our sFPDP core is unique in that we support nearly all transceiver-based devices from Intel/Altera, Xilinx, and Microsemi. We’re always making improvements to the core and adding support for new FPGA device families. Our core provides an open interface to the FPGA transceiver, giving the user complete control over transceiver speed, settings and adjustments. A complete reference design is provided for each family, as well as a thorough testbench with support for Riviera and ModelSim tools. In addition, our testing procedure includes exhaustive interoperability testing among all FPGA families and manufacturers to ensure compatibility.

StreamDSP is committed to delivering the highest level of customer support to ensure smooth system integrations. We also offer IP core customization and FPGA design services.

Learn more about sFPDP IP core

This paper presents challenges of gate count estimation during early architecture design phase along with effective methodology. This paper is backed up with vast experience of various IP designs with logic area up-to several hundreds of kilo gates with several hundred kilo bits of memory.