SENT/SAE J2716 Receiver

The CSENT-RX core implements a receiver for the Single Edge Nibble Transmission (SENT) protocol.

Overview

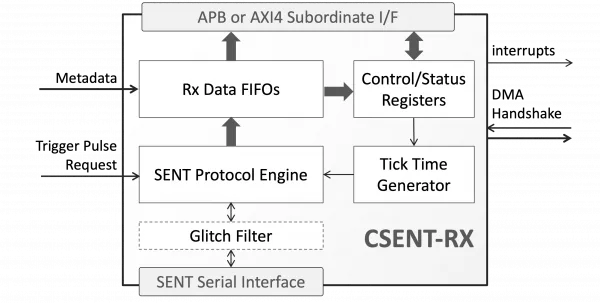

The CSENT-RX core implements a receiver for the Single Edge Nibble Transmission (SENT) protocol. It complies with the SAE J2716 standard and supports both synchronous and asynchronous sensors. It can be used for receiving data from one or multiple sensors using a single SENT line. The CSENT-RX provides access to its control, status, and data registers via a 32-bit APB, or AXI4-Lite bus interface, and the reset values for all its control registers are defined at synthesis time. The core provides a glitch filter on the serial data input and has data mapping functionality on received data to offload the connected host from data formatting. An external metadata port allows the host system to add customized metadata (e.g. timestamps) into the received data stream. The received data are accessible via the register interface. The core is also capable of generating trigger pulses requesting synchronous sensors to send data. The generation of trigger pulses is controlled via a dedicated input pin, or via a control register. A set of handshaking signals facilitates the integration with an external DMA controller. An extended set of interrupt sources includes detection of calibration variation, timeout errors, frequency drift error, FIFO-related triggers, frames’ validity and numerous frame’s errors. The CSENT-RX core is designed with industry best practice, has been rigorously verified and is production proven.

SENT/SAE J2716 Receiver

- Fast and Slow Channel

- 4, 6 or 8-bit CRC checking

- Programmable Glitch filter

- All types of SENT Frames

- Programmable data length (1 to 8 nibbles) for Fast Channel Frames

- Short (8-bit data) and Enhanced (12- or 16-bit data) Message Formats for Slow Channel

- Fast Channel data mapping to reduce host/CPU overhead

- Customized metadata support

- Supports inverted SENT protocol

Trigger Pulse for Synchronous Sensors

- Allows up to four sensors (transmitters) to use the same physical SENT connection

- Programmable trigger pulse length

- Activated via software or hardware

Ease of Integration

- 32-bit APB or AXI4-Lite interface, and comprehensive set of interrupts

- Programmable reference counter to validate calibration pulses

- Optional Receive FIFO of configurable size for Fast Channel data

- Run-time programmable configuration registers

- Synthesis-time defined reset values for all registers, enables data reception without control from host processor

- LINT-clean, single-clock domain, scan-ready design

Block Diagram

What’s Included?

- RTL source code or targeted FPGA netlist

- SystemVerilog Testbench

- Sample synthesis and simulation scripts

- Documentation

- IP XACT register definitions

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SENT IP core

Integrating PQC into StrongSwan: ML-KEM integration for IPsec/IKEv2

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Accelerating PCIe Gen6 L0p Verification for AI & HPC Designs using Synopsys VIP

Morgan State University (MSU) Leveraging Intel 16 and the Cadence Tool Flow for Academic Chip Tapeout

UEC-LLR: The Future of Loss Recovery in Ethernet for AI and HPC

Frequently asked questions about SENT IP cores

What is SENT/SAE J2716 Receiver?

SENT/SAE J2716 Receiver is a SENT IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this SENT?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SENT IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.