Scatter Gather DMA Engine - Validates efficient scatter-gather DMA for high-performance data transfer

The Scatter-Gather DMA Engine Verification IP (VIP) is designed to validate the functionality and performance of scatter-gather D…

Overview

The Scatter-Gather DMA Engine Verification IP (VIP) is designed to validate the functionality and performance of scatter-gather DMA controllers in SoCs. It ensures efficient data transfer between non-contiguous memory regions while minimizing CPU utilization, offering features like protocol compliance and transaction monitoring.

Ideal for applications such as networking, multimedia, storage, and embedded systems, the VIP helps ensure high-performance, reliable data movement. It supports multi-channel configurations, error injection, and performance monitoring to optimize system efficiency and robustness

Key features

- Flexible Descriptor Management: Supports dynamic descriptor chains for handling non-contiguous memory regions. Ensures efficient data transfers across varying buffer configurations, improving overall memory management.

- High Throughput Validation: Simulates high-speed data transfers with minimal CPU intervention. Verifies that DMA operations are efficient and capable of handling large volumes of data.

- Protocol Compliance Checking: Validates adherence to standard DMA protocols, ensuring correct signaling and timing. This prevents communication errors between DMA controllers and memory systems.

- Error Injection Capabilities: Allows for fault tolerance testing by injecting errors such as checksum issues or misaligned memory accesses. Verifies the robustness of the DMA controller’s error recovery mechanisms.

- Multi-Channel Support: Verifies the simultaneous operation of multiple DMA channels. Ensures proper arbitration, channel prioritization, and resource allocation for multi-threaded applications.

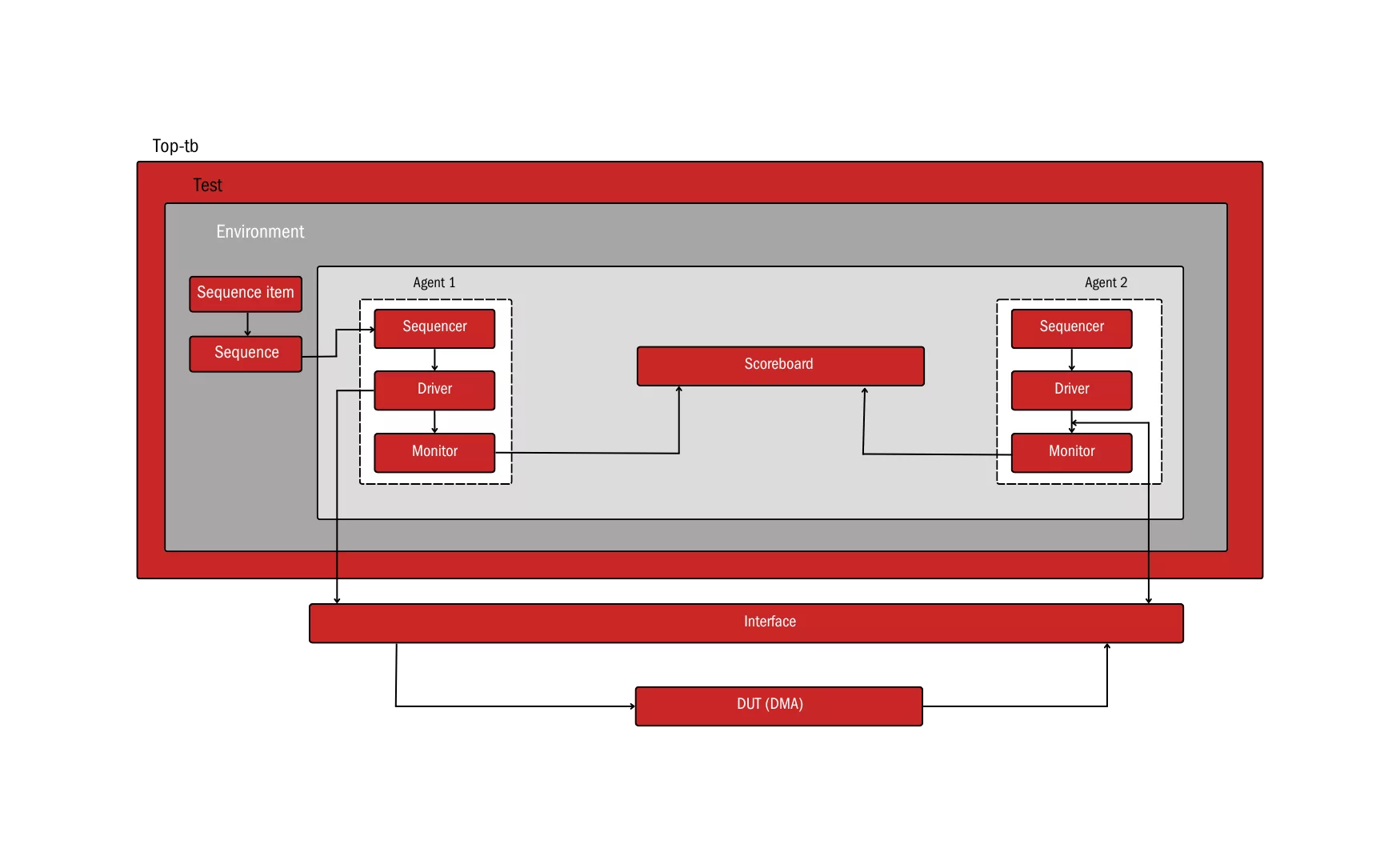

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DMA IP core

Using peripheral DMA boosts networked 32 bit MCU security and bandwidth

New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

Considerations When Architecting Your Next SoC: NoCs with Arteris

Can Your NPU Run DOOM? Chimera Can.

Frequently asked questions about DMA IP

What is Scatter Gather DMA Engine - Validates efficient scatter-gather DMA for high-performance data transfer?

Scatter Gather DMA Engine - Validates efficient scatter-gather DMA for high-performance data transfer is a DMA IP core from XtremeSilica listed on Semi IP Hub.

How should engineers evaluate this DMA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DMA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.