Programmable Root of Trust with Quantum Safe Cryptography acceleration and DPA-resistant & FIA-protected cryptographic accelerators

The CryptoManager RT-6xx v3 Root of Trust family from Rambus is the latest generation of fully programmable FIPS 140-3 compliant …

Overview

The CryptoManager RT-6xx v3 Root of Trust family from Rambus is the latest generation of fully programmable FIPS 140-3 compliant hardware security cores offering Quantum Safe security by design for data center and other highly secure applications.

Device and system architects face a growing array of security threats, including the threat of quantum computers. Across applications, one constant is the need for a hardware Root of Trust-based security implementation.

The CryptoManager RT-6xx family protects against a wide range of hardware and software attacks through state-of-the-art side channel attack countermeasures and anti-tamper and security techniques. The RT-6xx supports various security certifications up to level 3. The RT-6×4 Root of Trust adds Quantum Safe Encryption (QSE) to provide a future-proof hardware security solution to protect data center assets starting today and into the quantum era.

The RT-6xx allows customers to develop secure and trusted applications that run securely within a trusted boundary. Secure applications can be assigned unique roots and keys, allowing independent permissions and access levels.

How the CryptoManager RT-6xx Root of Trust Works

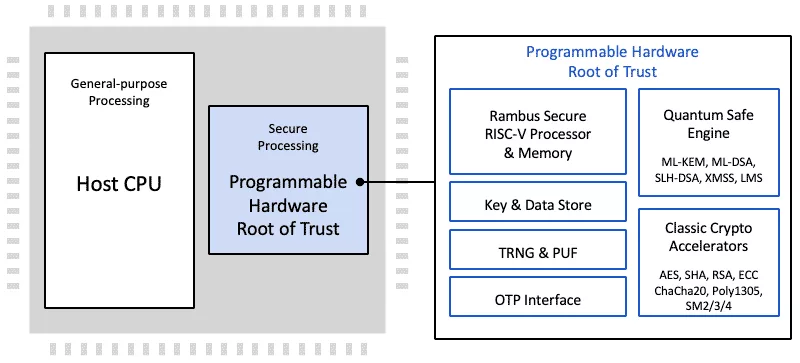

The CryptoManager RT-6xx Root of Trust is a siloed hardware security IP core for integration into semiconductors, offering secure execution of authenticated user applications, tamper detection and protection, secure storage and handling of keys and security assets, and optional resistance to side-channel attacks. The Root of Trust is easily integrated with industry-standard interfaces and system architectures and includes standard hardware cryptographic cores. Access to crypto modules, keys, memory ranges, I/O, and other resources is enforced in hardware. Critical operations, including key derivation and storage, are performed in hardware with no access by software. The Root of Trust is based on a custom 32-bit processor designed specifically to provide a trusted foundation for secure processing on chip and in the system. The RT-6xx inherits its flexible cryptographic accelerator from the embedded Rambus CryptoManager Hub CH-6xx cores.

The Root of Trust supports all common host processor architectures including ARM, RISC-V, x86 and others. The multi-threaded secure processor runs customer developed signed code either as a monolithic supervisor or as loadable security applications which include permissions and security-related metadata. It can implement standard security functionality provided by Rambus, or complete customer-specific security applications, including key and data provisioning, security protocols, biometric applications, secure boot, secure firmware update, and many more.

Key features

- Custom-designed, customer programmable 32-bit secure RISC-V processor

- AXI Interface to SoC, and fast 64-bit addressable DMA to host memory

- Multi-layered security model protecting all core components against a wide range of attacks. The security model includes hierarchical privilege model, secure key management policy, hardware-enforced isolation/access control/protection, error management policy

- Secure data store allowing assets generated during boot available for secure applications

- Wide range of classic and Quantum Safe cryptographic accelerators and security modules, such as canary logic for protection against glitching and overclocking, secure key derivation

- State-of-the-art anti-tamper mechanisms against DPA and FIA side channel attacks

Block Diagram

What’s Included?

- Complete Documentation

- Integration guides

- Reference manuals

- Programming guides

- Optional FIPS 140-3 support package

- RTL and FW Package

- Verilog RTL for synthesis and simulation

- Standard EDA tool flow scripts and support files

- Verification test bench and test vectors

- Boot loaders and secure RTOS and security monitor firmware

- HLOS APIs for accessing RT-6xx capabilities

- SW SDK Package

- SDK including the development environment, complete emulation with debugging capabilities of the RISC-V and crypto cores on QEMU

- One-step install emulation with multiple samples and reference code to help customers kickstart their secure application development

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Root Of Trust IP core

Rambus CryptoManager Root of Trust Solutions Tailor Security Capabilities to Specific Customer Needs with New Three-Tier Architecture

Why Anti-tamper Sensors Matter: Agile Analog and Rambus Deliver Comprehensive Security Solution

Side-Channel Attacks On Post-Quantum Cryptography

Cryptography Does Not Equal Security

Root of Trust: A Security Essential for Cyber Defense

Frequently asked questions about Root of Trust IP cores

What is Programmable Root of Trust with Quantum Safe Cryptography acceleration and DPA-resistant & FIA-protected cryptographic accelerators?

Programmable Root of Trust with Quantum Safe Cryptography acceleration and DPA-resistant & FIA-protected cryptographic accelerators is a Root Of Trust IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Root Of Trust?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Root Of Trust IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.