RLDRAM2 Synthesizable Transactor provides a smart way to verify the RLDRAM2 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's RLDRAM2 Synthesizable Transactor is fully compliant with standard RLDRAM2 Specification and provides the following features.

RLDRAM2 Synthesizable Transactor

Overview

Key Features

- Supports 100% of RLDRAM2 protocol standard

- Supports all the RLDRAM2 commands as per the specs

- Supports the following devices:

- X9

- X18

- X36

- Supports 8 internal banks for concurrent operation and maximum bandwidth

- Supports reduce cycle time (15ns at 533MHZ)

- Supports non multiplexed addresses (address multiplexing option available)

- Supports SRAM-type interface

- Supports programmable read latency (RL), row cycle time, and burst sequence length

- Supports balanced read and write latencies in order to optimize data bus utilization

- Supports data mask for write commands

- Supports data valid signal (QVLD)

- Supports on-die termination (ODT) RTT

- Supports IEEE 1149.1 compliant JTAG boundary scan

- Supports full-timing as well as behavioral versions in one model

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timings and protocol violations

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

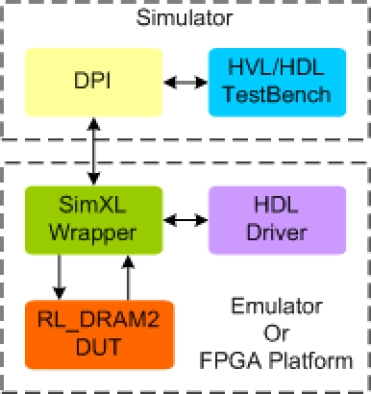

Block Diagram

Deliverables

- Synthesizable transactors

- Complete regression suite containing all the RLDRAM2 testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Technical Specifications

Short description

RLDRAM2 Synthesizable Transactor

Vendor

Vendor Name