Fast Quantum Safe Engine for ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) with DPA

The Quantum Safe Engine (QSE) IP provides Quantum Safe Cryptography acceleration for ASIC, SoC and FPGA devices.

Overview

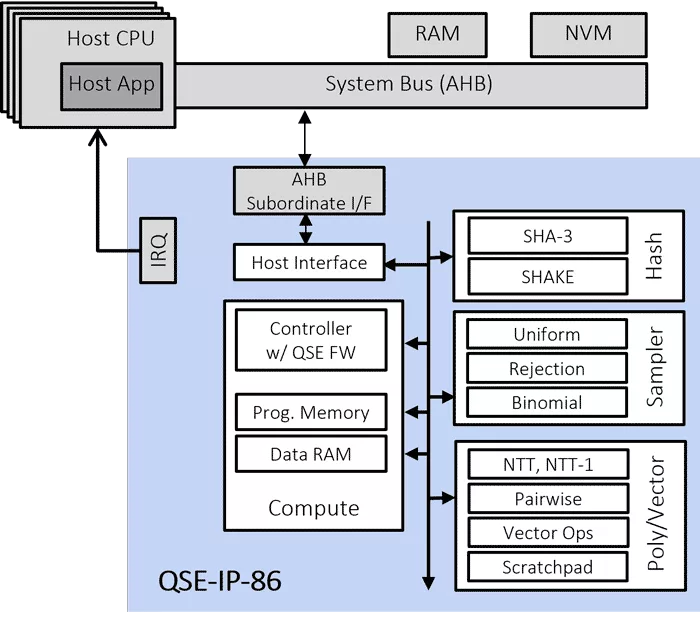

The Quantum Safe Engine (QSE) IP provides Quantum Safe Cryptography acceleration for ASIC, SoC and FPGA devices. The QSE-IP-86 core is typically integrated in a hardware Root of Trust or embedded secure element in chip designs together with a PKE-IP-85 core that accelerates classic public key cryptography and a TRNG-IP-76 core that generates true random numbers. For highly secure applications requiring additional protection against differential power analysis (DPA) attacks, a DPA version of the QSE is available.

The QSE supports the FIPS 203 ML-KEM and FIPS 204 ML-DSA standards. The embedded QSE core firmware allows the core functionality to be updated to adapt to potential future updates in the NIST specifications.

Key features

- Compliant with FIPS 203 ML-KEM and FIPS 204 ML-DSA standards

- Uses CRYSTALS-Kyber, CRYSTALS-Dilithium quantum-resistant algorithms

- Includes SHA-3, SHAKE-128 and SHAKE-256 acceleration

- The embedded QSE CPU combined with Rambus-supplied firmware implements the full FIPS 203/204 protocols

- Can be used stand alone or integrated into higher function security cores

- Offered as standard QSE-IP-86 or as DPA-protected QSE-IP-86-DPA

- Supports ASIC, SoC and FPGA implementations

- Firmware programmable to allow updates with evolving quantum-resistant standards

Block Diagram

What’s Included?

- Complete Documentation

- Integration guides

- Reference manual

- Application developer guide

- RTL and FW Package

- Verilog RTL for synthesis and simulation

- Standard EDA tool flow scripts and support files

- Verification test bench and test vectors

- SW Package

- Driver Development Kit, including examples

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Post Quantum IP core

Mitigating Side-Channel Attacks In Post Quantum Cryptography (PQC) With Secure-IC Solutions

How to design secure SoCs Part IV: Runtime Integrity Protection

Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

Providing protection against EMFI attacks

Deploying StrongSwan on an Embedded FPGA Platform, IPsec/IKEv2 on Arty Z7 with PetaLinux and PQC

Frequently asked questions about Post-Quantum Cryptography IP cores

What is Fast Quantum Safe Engine for ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) with DPA?

Fast Quantum Safe Engine for ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) with DPA is a Post Quantum IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Post Quantum?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Post Quantum IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.