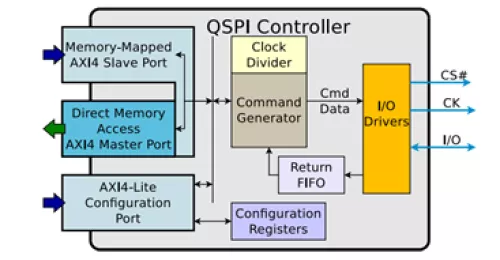

Arasan Chip Systems Quad SPI (QSPI) master core is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the majority of QSPI devices standard from a standard AXI4 slave interface. It also features support for Octal SPI, Dual SPI (DSPI), and SPI interface. The core is designed so that a user design may immediately access memory from the QSPI device in SPI mode, or alternatively issue a command to switch to any other mode. Additionally, a DMA command may be issued to copy memory from the QSPI device to anywhere else on the bus.

Quad SPI Master IP

Overview

Key Features

- Compliant with AMBA AXI3/4 and AXI4-lite protocols. An APB control port interface is available if desired instead of the AXI4-lite control port interface.

- User configurable clock frequency support

- Designed to support all leading NOR FLASH devices.

- Configurable bus width, Full & Narrow AXI burst support

- DMA for maximum bus throughput

- Supports 24 or 32b addressing and User selectable commands.

- Supports Execute in Place flash access protocols

- Backwards compatible with SPI and Dual SPI devices

Block Diagram

Technical Specifications

Maturity

Silicon proven