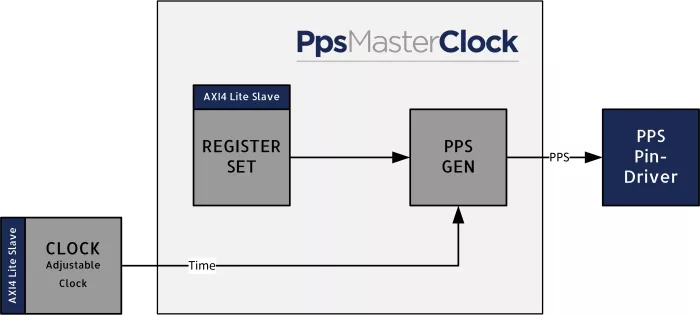

NetTimeLogic’s PPS Master Clock is a full hardware (FPGA) only implementation of a synchronization core able to synchronize other nodes to a Pulse per Second output based on a reference time. The whole algorithms and calculations are implemented in the core, no CPU is required. This allows running PPS synchronization completely independent and standalone from the user application. The core can be configured either by signals or by an AXI4Light-Slave Register interface.

All calculations and corrections are implemented completely in HW.

Pulse Per Second Master (PPS) core

Overview

Key Features

- PPS Master Clock

- Output delay compensation

- PPS duty cycle adjustment, width can be set via register

- AXI4 Light register set or static configuration

- PPS resolution with 50 MHz system clock: 10ns

Benefits

- Coprocessor handling PPS synchronization standalone in the core.

- Simple interface

Block Diagram

Applications

- Distributed data acquisition

- Ethernet based automation networks

- Automation

- Robotic

- Automotive

- Test and measurement

Deliverables

- Source Code (not encrypted, not obfuscated)

- Reference Designs

- Testbench with Stimulifiles

- Configuration Tool

- Documentation

Technical Specifications

Short description

Pulse Per Second Master (PPS) core

Vendor

Vendor Name

Availability

Now

Related IPs

- Pulse Per Second Slave (PPS) core

- Pulse Per Second (PPS) Clock to PPS core

- RFFE Master IP Core

- Serial Peripheral Interface (SPI) Master Module

- High-performance microcontroller core with a 12-stage dual-issue out-of-order pipeline and a high performance FPU

- Compact, Secure and Performance Efficiency 32-bit RISC-V Core