Protocol controller IP for Classical CAN / CAN FD / CAN XL

The X_CAN is the new CAN Communication Controller IP supporting CAN XL protocol.

Overview

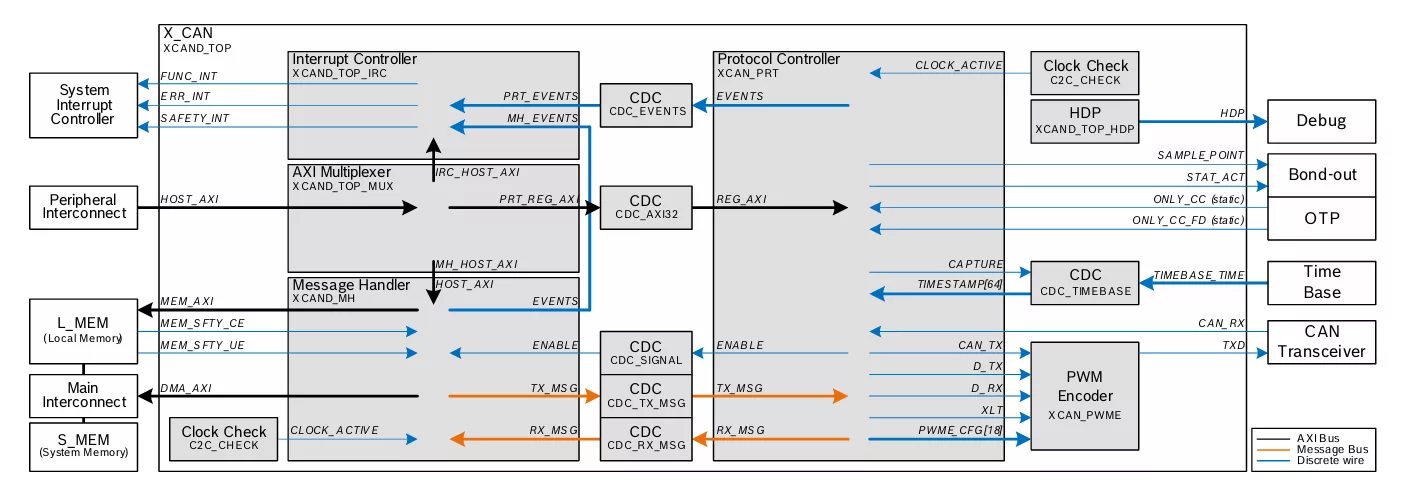

The X_CAN is the new CAN Communication Controller IP supporting CAN XL protocol. It can be integrated as part of a SoC. It is described in VHDL on RTL level, prepared for synthesis. The X_CAN performs communication according to ISO11898-1:2015 and CiA610-1.

The X_CAN can be connected to a wide range of HOST CPUs via its 32bit interface. The clock domain concept allows the separation between the high precision CAN clock and the HOST clock, which may be generated by an FM-PLL.

Key features

- Conform with ISO11898-1:2015 and CiA610-1

- CAN CC (CAN classic) with up to 8 data bytes and up to 1Mbit/s

- CAN FD (CAN flexible data rate) with up to 64 data bytes and up to 8Mbit/s

- CAN XL (CAN extended data length) with up to 2048 data bytes and up to 20Mbit/s

- 1 Priority Queue, up to 32 slots, priority based on the arbitration field of the CAN frame

- 8 TX FIFO queues, each with up to 1024 messages

- 8 RX FIFO queues, each with up to 1024 messages

- TX message filtering with up to 16 filter elements

- RX message filtering with up to 255 filter elements, while each can compare one 32bit word (The actual usable number of filter elements depends on CAN clock frequency, CAN bit rate, and Local Memory performance)

- Internal DMA engine, X_CAN is the DMA master for message handling

- Message storage in system memory

- Low CPU impact, any accesses to/from the system memory are done using the internal DMA engine (less interrupts needed)

- Requires only small local memory

- Approx 4Kbytes for up to 255 RX filter elements

- Multiple X_CAN can share the same Local Memory

- Maskable module interrupts with three categories: Functional, Functional Error and Safety

- Three clock domains (HOST, CAN, TIMEBASE clock domains)

- CAN Error Logging

- Fault Injection Module

- Programmable loop-back test mode

- Power-down support

- AXI4-Lite slave interface (HOST_AXI) (compliant to AMBA 4 ARM Ltd protocol, see [5])

- AXI4 master DMA interface (DMA_AXI) (compliant to AMBA 4 ARM Ltd protocol, see [5])

- AXI4 master Local Memory interface (MEM_AXI) (compliant to AMBA 4 ARM Ltd protocol, see [5])

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is Protocol controller IP for Classical CAN / CAN FD / CAN XL?

Protocol controller IP for Classical CAN / CAN FD / CAN XL is a CAN / CAN-FD / CAN-XL IP core from Robert Bosch GmbH listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.