Protocol controller IP for CAN / CAN FD

The M_CAN module is the new CAN Communication Controller IP-module that can be integrated as stand-alone device or as part of an …

Overview

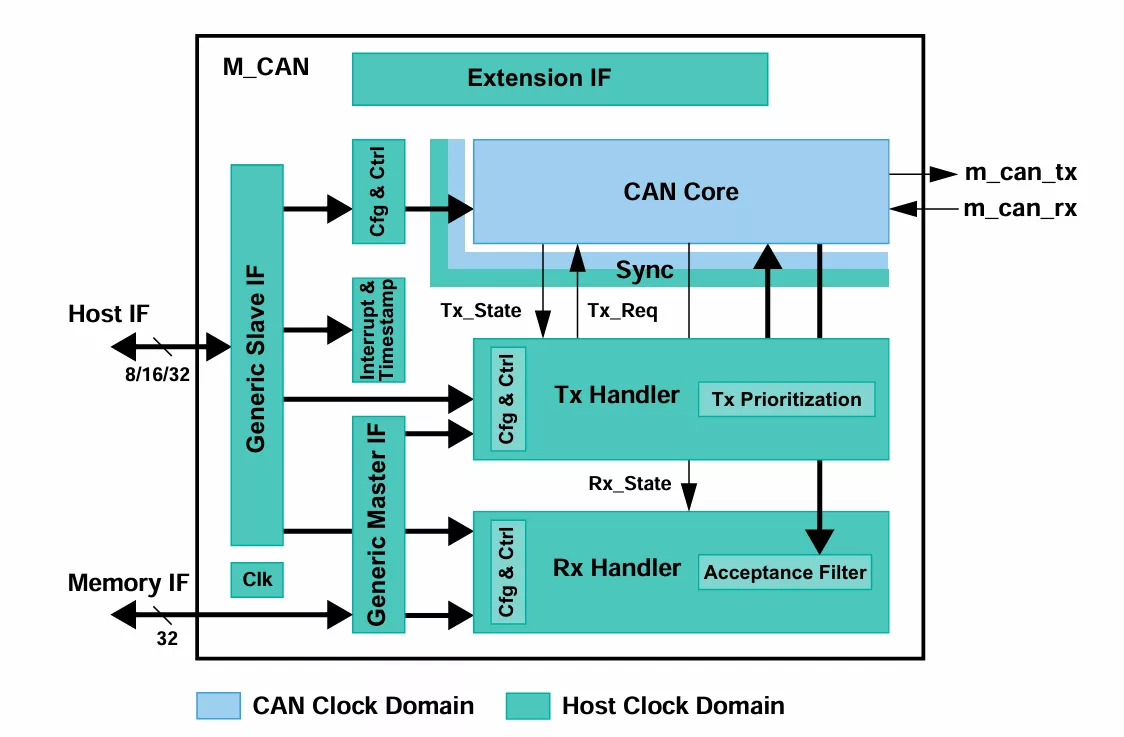

The M_CAN module is the new CAN Communication Controller IP-module that can be integrated as stand-alone device or as part of an ASIC. It is described in VHDL on RTL level, prepared for synthesis. The M_CAN performs communication according to ISO 11898-1:2015. Additional transceiver hardware is required for connection to the physical layer.

The message storage is intended to be a single- or dual-ported Message RAM outside of the module. It is connected to the M_CAN via the Generic Master Interface. Depending on the chosen ASIC integration, multiple M_CAN controllers can share the same Message RAM.

All functions concerning the handling of messages are implemented by the Rx Handler and the Tx Handler. The RxHandlermanagesmessageacceptancefiltering,thetransferof received messages from the CAN Core to the Message RAM as well as providing receive message status information. The Tx Handler is responsible for the transfer of transmit messages from the Message RAM to the CAN Core as well as providing transmit status information.

Acceptance filtering is implemented by a combination of up to 128 filter elements where each one can be configured as a range, as a bit mask, or as a dedicated ID filter.

The M_CAN can be connected to a wide range of Host CPUs via its 8/16/32-bit Generic Slave Interface. The M_CAN’s clock domain concept allows the separation between the high precision CAN clock and the Host clock, which may be generated by an FM-PLL.

Key features

- Conform with ISO 11898-1:2015

- CAN FD with up to 64 data bytes supported

- CAN Error Logging

- AUTOSAR support

- SAE J1939 support

- Improved acceptance filtering

- Two configurable Receive FIFOs

- Separate signalling on reception of High Priority Messages

- Up to 64 dedicated Receive Buffers

- Up to 32 dedicated Transmit Buffers

- Configurable Transmit FIFO

- Configurable Transmit Queue

- Configurable Transmit Event FIFO

- Direct Message RAM access for Host CPU

- Multiple M_CANs may share the same Message RAM

- Programmable loop-back test mode

- Maskable module interrupts

- 8/16/32 bit Generic Slave Interface for connection customer-specific Host CPUs

- Two clock domains (CAN clock and Host clock)

- Power-down support

- Debug on CAN support

- DMA Support (DMU add-on required)

- Support of Hardware Timestamping according to CiA 603 (TSU add-on required)

Block Diagram

What’s Included?

- Deliverables for ASIC design

- Well documented VHDL source code

- VHDL test bench environment

- M_CAN User’s Manual (programmer's view)

- M_CAN System Integration Guide (designer's view)

- M_CAN Module Integration Guide (designer's view)

- M_CAN Conformance Test Report

- Deliverables for FPGA design

- Encrypted VHDL source code

- VHDL source code of an example system design with RAM and an example arbiter instance

- Source code FPGA internal bus interface

- M_CAN User’s Manual (programmer's view)

- M_CAN System Integration Guide (designer's view)

- M_CAN FPGA Integration Guide (designer's view)

- M_CAN Conformance Test Report

- Programming examples for fast start up

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is Protocol controller IP for CAN / CAN FD?

Protocol controller IP for CAN / CAN FD is a CAN / CAN-FD / CAN-XL IP core from Robert Bosch GmbH listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.