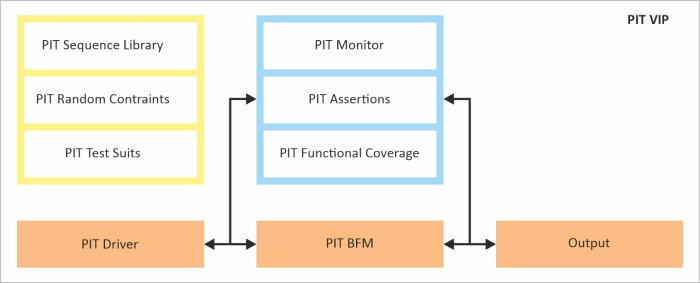

The PIT Verification IP provides a simple verification solution to verify the components interfacing with the PIT the VIP supports Verilog and System Verilog with Universal Verification Methodology (UVM). PIT compatible UVM based, a BUS monitor. BUS monitor monitors all the transfers that are going on the PIT bus.

PIT Verification IP

Overview

Key Features

- The programmable interval timer module (PIT) contains clock select logic, up counter, a modulo register, and a control register.

- Support With Different Counting Mode i.e count up and count down.

- Support Interrupt generation.

- Support multiple clock sources, including selectable clock prescalers.

- Support Count Modulo.

- Support DMA trigger pulses.

- Support independent timeout periods for each timer.

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure highest levels of quality.

- Availability of Conformance and Regression Test Suites.

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

Block Diagram

Deliverables

- PIT Driver

- PIT Monitor

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic Test Suite

- Random Test Suite

- Error Test Suite

- Assertions & Cover Point Tests