OSU processor, optimized for E1/FE/GE services with Ethernet over SDH over OTU0/OTU1 lines

The TPS3215MP OSU processor is an IP Core solution designed for Xilinx FPGAs.

Overview

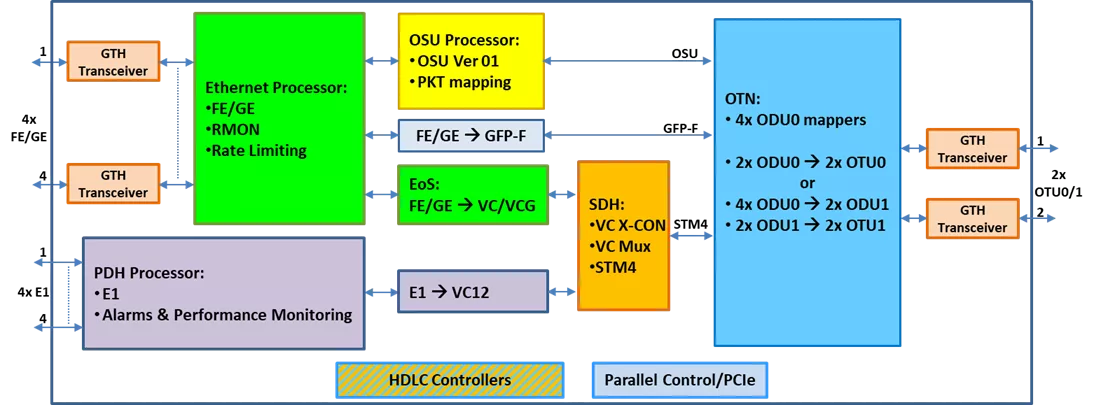

The TPS3215MP OSU processor is an IP Core solution designed for Xilinx FPGAs. TPS3215MP processors accept 4x FE/GE and 4x E1 client signals, process and present them to either SDH VC, OSU or ODU containers for their transport over OTU0/OTU1 bearers. TPS3215MP processors include an Ethernet-over-SDH (EoS) capability. The OTU line signals can be configured in 1+1 protection configurations, offering protection at the OTU/ODU/OSU/SDH levels. For Ethernet client-services, Ethernet rate-limiting is provided. TPS3215MP processors support hitless bandwidth adjustment of OSU containers carrying Ethernet information. Integrated HDLC controllers can be assigned to GCC in-band communications channels. TPS3215MP processors are offered as complete turn-key solutions for Xilinx FPGAs, including built-in jitter attenuators.

Key features

- Line Signals: 2x OTU0/1

- Protection: 1+1 at the OTU/ODU/OSU/VC levels

- Integrated HDLC controllers for GCC channels

- Client Signals: 4x FE/GE and 4x E1

- Built-In jitter attenuators for Line and Client signals

- Mapping of client signals to OSU/ODU/VC transport containers

- Alarms and Performance Counters for Client/Line signals.

- Ethernet Rate-Limiting

- Ethernet-over-SDH (EoS): FE/GE mapping to SDH Virtual Containers (VCs)

- SDH: STM4 signal

- Maintenance: Loopbacks, PRBS generation and monitors

- Control: PCIe/Parallel

Block Diagram

Benefits

- Single-Chip (IP Core) solution for OSU-based OTN Remote Terminals (RT)

- Optimizes line-side bandwidth thanks to SDH VC and OSU transport containers

- Interoperability with legacy SDH infrastructure: Built-In Ethernet-over-SDH

- Supports Tri-Mix capability for Ethernet client-signals: Mapping of FE/GE to SDH VC/OSU/ODU transport containers

- Rate-Limiting for Ethernet client-services

- Seamless integration with the existing G.709 OTN infrastructure

Applications

- OSU based remote terminals

What’s Included?

- Bin File with Security key

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Optical Transport IP core

Encrypting Telecoms

TPACK's role in Altera designs

Part 2: Opening the 5G Radio Interface

How 224G SerDes Unifies Today’s AI Fabrics

Securing the Future of Terabit Ethernet: Introducing the Rambus Multi-Channel Engine MACsec-IP-364 (+363)

Frequently asked questions about Optical Transport IP cores

What is OSU processor, optimized for E1/FE/GE services with Ethernet over SDH over OTU0/OTU1 lines?

OSU processor, optimized for E1/FE/GE services with Ethernet over SDH over OTU0/OTU1 lines is a Optical Transport IP core from Tera-Pass listed on Semi IP Hub.

How should engineers evaluate this Optical Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Optical Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.