NVMe over TCP IP core - End-to-End NVMe-oF TCP connectivity with no CPU!

NVMeTCP IP is the standalone host side NVMe Over Fabric (NVMe/TCP) controller with no CPU and external memory required.

Overview

NVMeTCP IP is the standalone host side NVMe Over Fabric (NVMe/TCP) controller with no CPU and external memory required. Enabling very high-performance remote access to NVMe-oF Storage Server by simple user logic. Greatly reduce design complexity and development time. Allowing your FPGA Card/Board to get access to the existing NVMe-oF storage infrastructure remotely and directly over FPGA’s network interface with maximum possible performance.

Key features

- NVMe/TCP (NVMe over TCP) host controller (Initiator), based on NVMe-oF specification rev 1.1 and NVMe specification rev 1.4

- Access one NVMe SSD on the target (Subsystem), selected by NVMe name (NQN)

- Command: Write and Read

- High performance:

- NVMeTCP25G-IP: Write = 2500MB/s, Read = 2600MB/s (1MB buffer)

- NVMeTCP10G-IP: Write = 1200MB/s, Read = 1200MB/s (1MB buffer)

- Data interface: Memory-mapped interface

- Data size per command: Fixed at 4 Kbytes

- Maximum command: 256 or less, limited by Read buffer size for Read command

- Configurable Read buffer size: 32Kbytes (up to 8 Read Cmd) - 1Mbytes (up to 256 Read Cmd)

- Supported NVMe/TCP target:

- IOCCSZ (I/O Queue Command Capsule Support Size): More than or equal to 4160 (1040h)

- MQES (Maximum Queue Entries Supported): More than or equal to 256 (100h)

- MAXCMD (Maximum Outstanding Commands): More than or equal to 256 (100h)

- Authentication: Not required

- Networking: 10Gb Ethernet speed in the same network for transferring ARP request/reply packet by using jumbo frame packet

- Ethernet MAC interface: 64-bit AXI4 Stream interface at 156.25 MHz

- User clock frequency: 156.25 MHz, the same clock as EMAC interface

- Available reference design: KCU105/ZCU102/ZCU106 board

- Customized service

- NVMe/TCP Target in different network that cannot transfer ARP packet to get Target MAC address

- The network that does not support jumbo frame packet

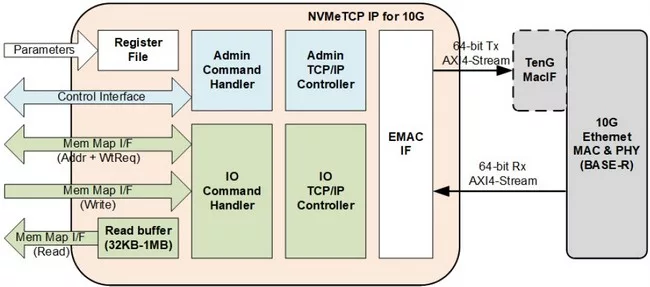

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is NVMe over TCP IP core - End-to-End NVMe-oF TCP connectivity with no CPU!?

NVMe over TCP IP core - End-to-End NVMe-oF TCP connectivity with no CPU! is a Ethernet IP core from Design Gateway Co., Ltd. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.