Baseband processor

The Ceva-BX2 baseband processor IP handles both signal-processing and control workloads with up to 16 GMACs per second performanc…

Overview

The Ceva-BX2 baseband processor IP handles both signal-processing and control workloads with up to 16 GMACs per second performance and high-level-language programming. It supports a range of integer and floating-point data types for a wide range of baseband applications like 5G PHY control, and exploits a high degree of parallelism, but with remarkably compact code size. Optimized high-speed interfaces expedite connection to other Ceva cores or to accelerators.

The Solution

The Ceva-BX2 combines the capabilities of signal processing and control-code execution into a single, compact DSP. Computational speed comes from quad-32×32/octal-16×16 MACs with added support for 16×8 and 8×8 MAC operations, organized into two parallel compute engines within an 11-stage pipeline. Each compute engine can add optional half- and single-precision IEEE floating-point units. These resources are directed by a five-way VLIW instruction set architecture with optimizations for single-instruction-multiple-data (SIMD) operation, including a hardware loop buffer for kernel execution. Efficient execution of control code is aided by dynamic branch prediction and a branch target cache. On signal-processing tasks the Ceva-BX2 can reach up to 16 GMACs per second, and on control workloads it can achieve up to 5.46 CoreMark/MHz. The hardware design is optimized for speed, achieving 2 GHz operation implemented in a TSMC 7nm process node with only common standard cells and memory compilers.

Key features

- 5-way VLIW architecture with quad 32×32 or octal 16×16 MACs and optional dual IEEE floating-point units

- Support for 8, 16, 32, and 64-bit integer operations, including 16×8 and 8×8 MAC operations for neural-network computations

- Sophisticated optimizations for control flow, including hardware loop buffer, branch target cache, and dynamic branch prediction

- Performance up to 16 GMACs per second and 5.46 CoreMark/MHz

- Hardware provisions for clustering multiple cores and for attaching coprocessors and accelerators

- Supported by LLVM compiler, Eclipse debug environment, and extensive software libraries

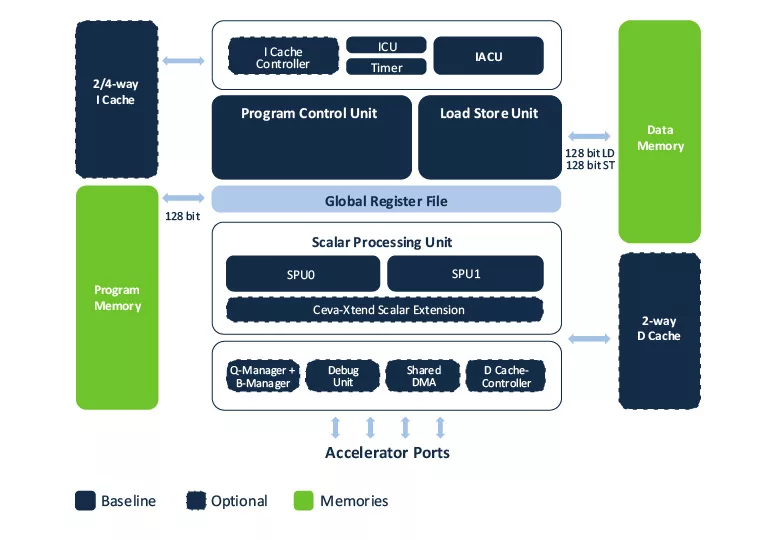

Block Diagram

Benefits

- The Ceva-BX2 combines the capabilities of a powerful compact DSP with those of a capable MCU, handling both signal-processing and control workloads in a single core. DSP performance is sufficient for 5G PHY control paths and other communications workloads. High-speed ports with optional automatic queuing and buffer controls make it easy to cluster Ceva-BX2 cores and to attach coprocessors and accelerators.

- The performance of the Ceva-BX2 can be achieved without assembly coding, using only C/C++ code with an LLVM compiler. The compiler, an RTOS, an Eclipse-based tool chain, extensive libraries for DSP and mathematical operations are all provided.

Applications

- Infrastructure

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Cellular IP core

CEVA-X1 DSP Core Targets Cellular IoT Opportunities

Video Messaging for ARM7-based Cellular Chipsets.

CEVA's XC12 DSP Core Targets Multi-Gbit Cellular, Wi-Fi Opportunities

SATCOM Adopting 3GPP Standards: From Proprietary Silos to Global Scale

Physical AI at the Edge: A New Chapter in Device Intelligence

Frequently asked questions about cellular IP cores

What is Baseband processor?

Baseband processor is a Cellular IP core from Ceva, Inc. listed on Semi IP Hub.

How should engineers evaluate this Cellular?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Cellular IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.