Arasan’s SPMI Device IP (Configurable Controller Cores) implements MIPI SPMI2.0 protocols. It is designed to be configured as a SPMI Host, SPMI Device Controller IPs.

Arasan’s SPMI Device IP is used to reduce power consumption in electronic devices to improve battery life and increase power budget for features such as color screens and backlights by accurately monitoring power performance level and control various supply voltages.

MIPI SPMI 2.0 Device IP

Overview

Key Features

- MIPI SPMI 2.0 Specifications Support

- Implements both SPMI 2.0 Host and SPMI 2.0 Device protocols

- Configurable to be used as a SPMI Host2.0 or SPMI Device 2.0 IP

- Supports both High-Speed (HS) 32KHz to 26MHz and Low Speed (LS), 32KHz to 15Mhz modes

- Supports multiple SPMI Host Arbitration modes (SCLK Handover, Arbitration Levels) and SPMI Device Arbitration Mode (Device request Holds)

- Supports Arbitration capable and non-arbitration capable Hosts as well as Request capable Device and Non-request capable Devices

- Advanced Features

- Calibration Core supports Bus Initialization, Bus disconnection, and Bus monitoring

- SPMI Host can operate as a Bus-owner, Connected Host or as a disconnected Host

- SPMI Host can decode all command frames including those marked as optional-to determine accurately end of sequence

- RAS Features

- Advanced Error Management unit support Parity Errors in Command frames, Address frames and Data frames

- Error handling mitigates errors due to Unsupported address, Unsupported Commands, Parity Error in Address and Data Frames

- Supports window-based SPMI traffic monitoring for debug

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers.

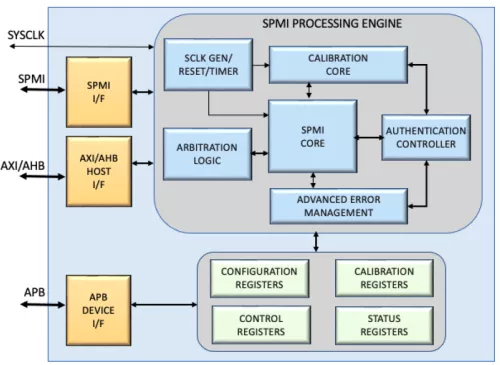

Block Diagram

Deliverables

- System Verilog RTL Source Code

- A simplified Testbench with simulation models to run initial set of tests after release

- Synthesizable Netlist

- Synthesis Scripts and exception lists

- Timing Report

- Protocol Compliance & Coverage Report

- Sample Firmware with Drivers

- Application Notes

Technical Specifications

Foundry, Node

TSMC & GF

Maturity

Silicon Proven

Availability

Now