The MIPI I3C Controller IP is compliant with the I3C specification and delivers higher bandwidth and scalability for integrating multiple sensors into mobile, automotive and IoT system-on-chips (SoCs) that previously depended on I2C. The support for in-band interrupts within the 2-wire interface provides a significantly lower pin count, simplifying board design and reducing power and cost. The I3C electrical characteristics enable faster data rates and lower power consumption than I2C by enabling push-pull mode of operation vs open drain mode in the Clock line and a large portion of the data line. The introduction of Common Command Codes (CCCs) help standardize the communication across controller and targets from different vendors.

The Target IP is backward compatible with I2C, allowing designers to future-proof their design whilst still interoperating with legacy and new sensors on a single I3C bus. The standard-based ARM® AMBA® Advanced Peripheral Bus (APB) connects the IP to the rest of the SoC while the bus is connected to the register interface and the Direct Memory Access (DMA) interface, offering easy IP integration.

The Target-Lite IP allows for low complexity and cost implementation intended for simple processor-less sensors/actuators to communicate/update their state with a host controller.

Low-power management features such as clock gating enable energy-efficient sensors and SoC designs while the configurable transaction and data buffering features allow performance versus cost trade-offs for the target application.

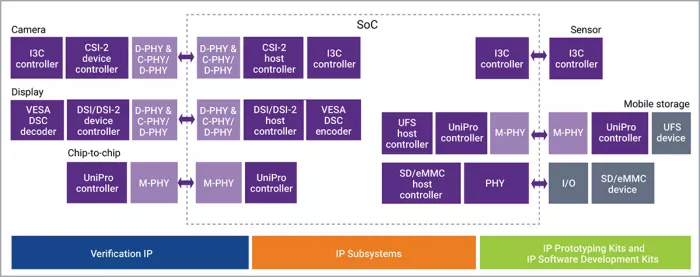

The MIPI I3C Controller IP with the vendor’ silicon-proven MIPI CSI-2 Controller, D-PHY, verification IP and IP Prototyping Kit enable designers to have a complete image sensor interface solution.

Besides acting as a sensor interface, the I3C IP natively supports the JEDEC JESD403-1 specification for DDR5 Sideband communication to connect the Host SoC with PMICs, RCDs and Temperature sensors on RDIMMs.

System Management standards such as Management Component Transport Protocol (MCTP) can be enabled as a layer above the I3C IP.

The vendor has digital IP, IO pads and VIP to make a comprehensive offering for I3C.