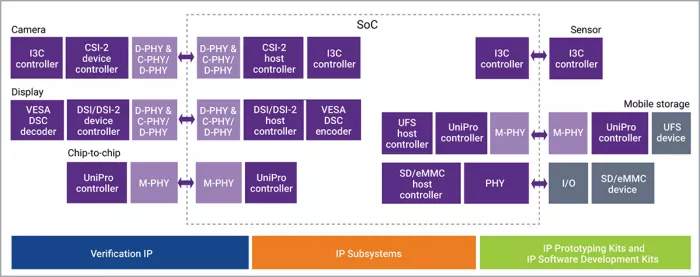

The integrated C-PHY/D-PHY IP enables high-performance, low-power interface to SoCs, application processors, baseband processors, and peripheral devices for mobile, automotive, artificial intelligence (AI), and IoT applications. The PHY, for FinFET processes and compliant with the MIPI C-PHY and D-PHY specifications, operates at 6.5Gb/s per lane and 6.5Gs/s per trio respectively for a maximum speed of 44.5Gb/s. The C-PHY/D-PHY addresses energy requirements by supporting low-power state modes and delivering below 1.2pJ/bit at the maximum speed. The PHY offers built-in test capabilities, including pattern generator, logic analyzer, and loopback modes covering all circuits. The C-PHY/D-PHY IP interoperates with the vendor’s ASIL B Ready ISO 26262 certified CSI-2 and DSI/DSI-2 controllers which support key features of the latest MIPI display and camera specifications.

MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes -TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

Overview

Key Features

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

- Aggregate throughput up to 44.5Gb/s in C-PHY mode and 26Gb/s in D-PHY mode

- Wide PHY Protocol Interface (PPI)

- Low-power escape modes and ultra low-power state modes

- Shutdown mode

- High speed BIST and at-speed scan test

- Primary, secondary, TX- and RX-only configurations

- Flexible input clock reference and lane/trio swap

- Silicon-proven, robust design available in advanced process technologies

Block Diagram

Technical Specifications

Short description

MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes -TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

Vendor

Vendor Name

Foundry, Node

TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

TSMC

Pre-Silicon:

5nm

Related IPs

- MIPI C-PHY v2.0 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes -TSMC N3A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- MIPI C-PHY v2.0 D-PHY v2.1 RX 2 trios/2 Lanes - TSMC N7 1.8V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- MIPI C-PHY v2.0 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC N7 1.8V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- MIPI C-PHY v1.2 D-PHY v2.1 RX 2 trios/2 Lanes - TSMC16FF 1.8V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- MIPI C-PHY v1.2 D-PHY v2.1 TX 3 trios/4 Lanes - TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2